使用Xilinx RFSoC器件发送和接收音调-第1部分系统设计

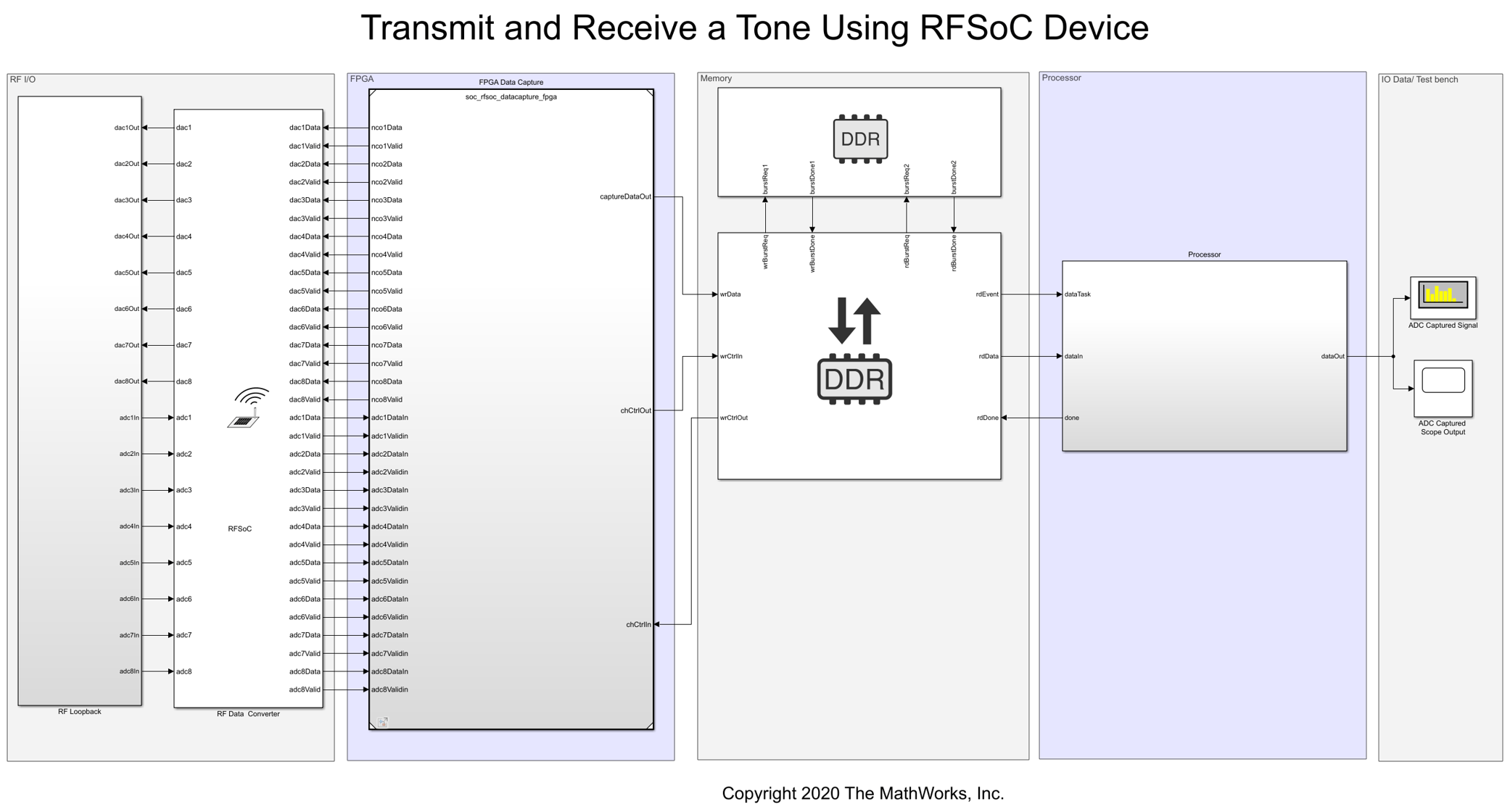

这个例子展示了如何使用SoC Blockset®为Xilinx®RFSoC设备设计数据路径。您将设计和模拟一个系统,该系统从FPGA生成一个正弦音调,并通过使用射频数据转换器(RFDC)块在多个射频信道之间传输音调。然后,系统将使用RFDC块将数据接收回FPGA,并使用嵌入式处理器一次将接收到的音调可视化为一个通道。

设计任务和系统说明

考虑在Xilinx RoSoC设备上需要以双工模式(GSP)数据速率访问多个RF信道的无线应用。在本例中,设计任务是从FPGA生成正弦音调,配置RFDC块,并按照以下系统规范在ZCU111和ZCU216评估套件上将数据接收回FPGA。

ZCU111评估试剂盒系统规格

ADC和DAC采样率= 2048 MSPS

ADC通道数=8

DAC通道数= 8

数字数据接口=真实

ZCU216评估试剂盒系统规格

ADC和DAC采样率=1024 MSPS

ADC通道数= 16

DAC通道数=16

数字数据接口= IQ

上述系统的设计和实施面临以下挑战:

配置RFDC块的多个参数值以满足系统需求比较困难。

由于数据速率高,在FPGA中设计同时操作多个样本的算法增加了设计的复杂性。

考虑到FPGA和处理器的异步特性,设计从FPGA到处理器的数据路径以满足给定的系统需求是困难的。

使用SoC块集进行设计

通过使用SoC块集提供的射频数据转换器块和外部内存块对系统进行建模,您将在实现之前模拟设计。模拟设计使您能够在实现硬件之前,在Simulink中识别和修复问题。金宝app

此设计示例包含两个顶级模型。

soc\u rfsoc\u数据捕获-通过ZCU111评估试剂盒8通道采集真实数据soc\u rfsoc\u IQ\u数据捕获\u顶部-通过ZCU216评估器采集16通道复杂IQ数据

这个例子展示了使用soc\u rfsoc\u数据捕获模型。工作流步骤对于这两种模型都是通用的。

创建一个SoC模型soc\u rfsoc\u数据捕获作为顶级车型,设置硬件板选项Xilinx Zynq Ultrascale+ RFSoC ZCU111评估试剂盒.该型号包括FPGA型号soc_rfsoc_datacapture_fpga处理器模型soc_rfsoc_datacapture_proc实例化为模型引用。顶层模型还包括内存通道和内存控制器块,它们在FPGA和处理器之间共享外部内存。

open_system (“soc_rfsoc_datacapture”)

close_system (“soc_rfsoc_datacapture”)

射频数据转换器配置

射频数据转换器模块为硬件逻辑中建模的无线算法提供了射频数据路径接口。您可以使用此块对adc和dac进行建模和配置,并将数据从硬件逻辑连接到硬件逻辑。该模块在Simulink中提供了与Xilinx射频数据转换器IP的接口,用于建模用于在Xilinx RFSoC设备上实现的无线系统。金宝app

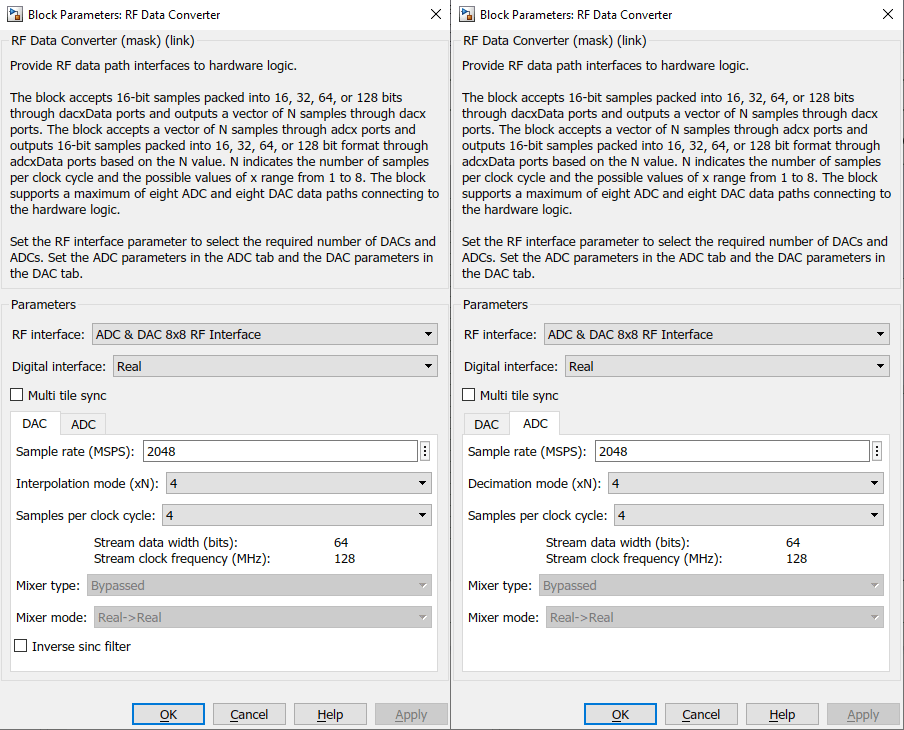

要满足2048 MSPS作为DAC和ADC数据速率的系统要求,必须选择插值模式,抽取模式,每个时钟周期的采样参数,使无线算法FPGA的有效时钟周期(采样率)在理想范围内。这是计算如下,并显示在块为流时钟频率你点击后申请.

对于本例,在DAC选项卡,设置插值模式和每个时钟周期的采样将参数值设置为4和模数转换器选项卡,设置抽取模式和每个时钟周期的采样参数值为4。这意味着流时钟频率to be 2048/(4*4) = 128 MHz。

RF数据转换器模块在左侧提供DAC的输出端口(dac1, dac2,等等,一直到dac8)和ADC的输入端口(adc1, adc2,等等,一直到adc8)。左侧端口信号是连接到FPGA的对应右侧信号的矢量化版本。对于本例,右侧DAC和ADC信号(dac1Data、dac2Data等,直到dac8Data和adc1Data、adc2Data等,直到adc8Data)每个(uint64)宽64位,左侧信号是对应右侧信号的4x1 int16向量版本。如果需要,这些端口可以用于无线信道的ADC和DAC之后的数据路径建模。对于本例,将DAC信号连接到ADC信号,以便将传输的信号环路回送。

硬件逻辑设计

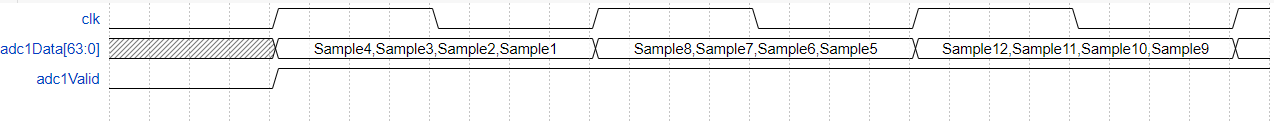

为了匹配RF Data Converter模块的DAC数字接口,硬件逻辑的发送路径必须每周期发送4个128 MHz时钟的采样。这张图显示了射频数据转换器模块的八个DAC数据接口之一的数据接口。正弦波音生成的采样率为512 MSPS (128 × 4)。

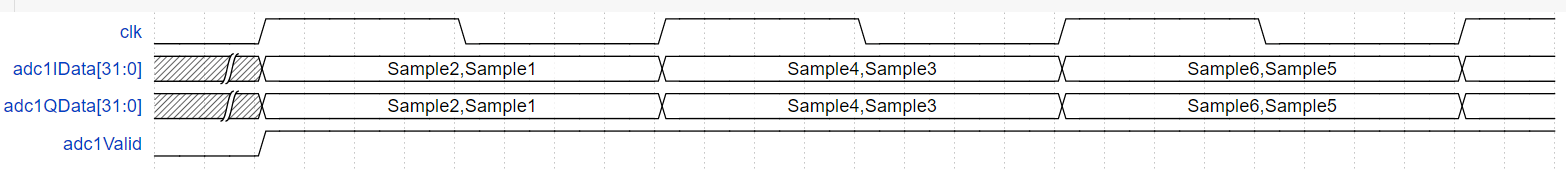

类似地,在接收端,算法必须在每个时钟周期上操作4个样本。这张图显示了射频数据转换块的八个ADC数据接口之一的数据接口。

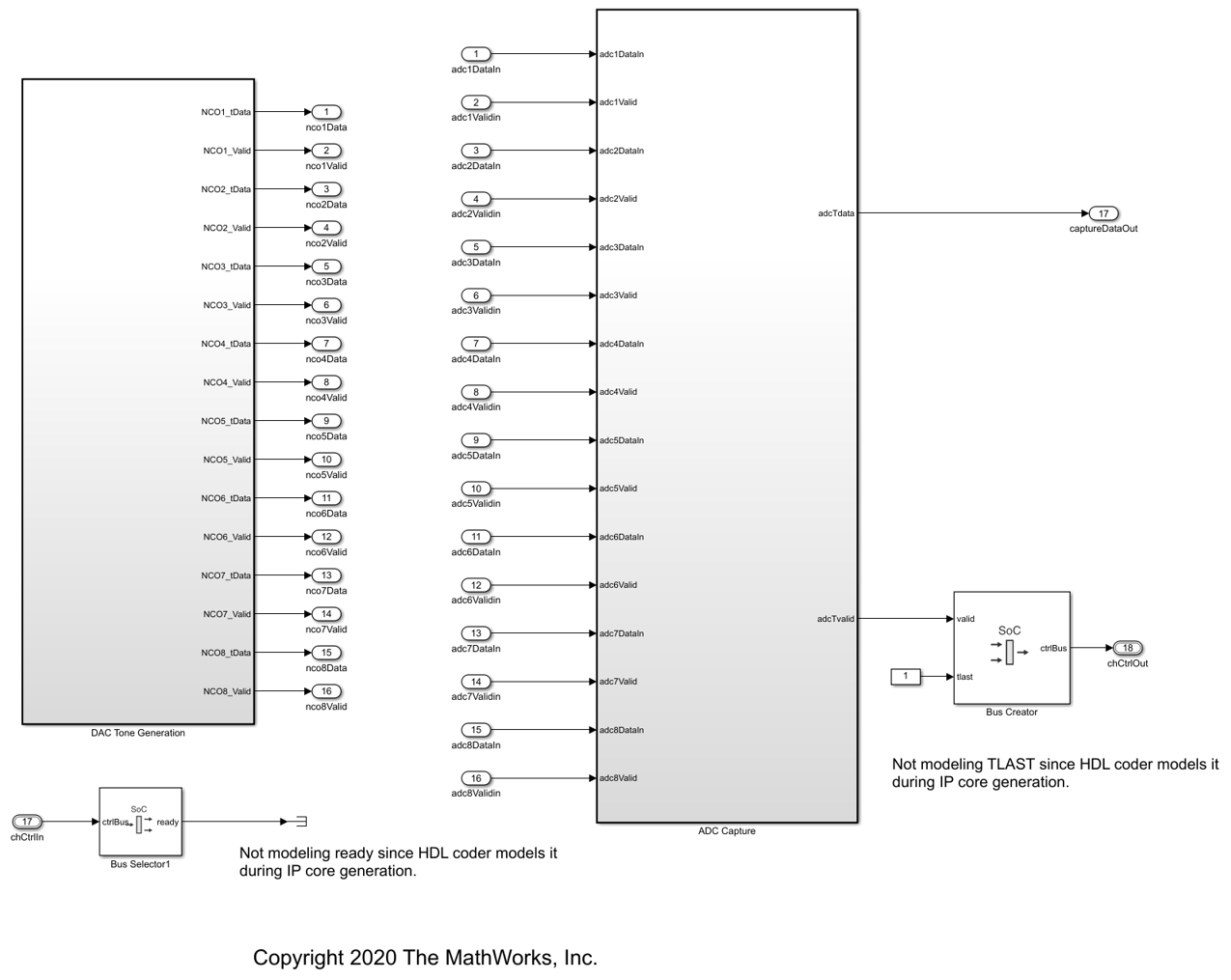

FPGA模型soc_rfsoc_datacapture_fpga包含两个子系统,DAC音调生成连接到RFDC块的DAC部分,ADC捕获子系统连接到ADC部分。通过使用四个HDL优化NCO块并为每个HDL优化NCO块选择不同的偏移量,并行生成四个连续的正弦波形样本。所有四个样本作为64位数据打包在一起,作为AXI流数据宽度。此外,在所有八个通道上传输相同的波形。每个通道由处理器设置为寄存器的不同比例因子进行缩放。

在ADC捕获子系统中,使用处理器设置的寄存器选择八个通道中的一个。从选定通道的数据在发送到处理器之前被下采样128。

open_system (“soc_rfsoc_datacapture_fpga”)

close_system (“soc_rfsoc_datacapture_fpga”)

处理器逻辑设计

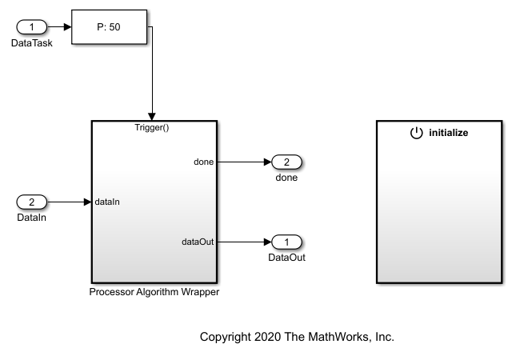

处理器逻辑包含一个基于事件的任务,该任务由来自FPGA的数据通过DDR内存到达驱动。处理器算法任务在任务管理器块中表示为dataTask,并指定为事件驱动的。任务管理器块通过缓冲区就绪事件异步调度数据,rdEvent在存储器通道中,表示从FPGA到达的一帧数据。算法本身在处理器模型中的Processor algorithm Wrapper子系统下建模soc_rfsoc_datacapture_proc并连接到顶层的任务管理器块。要对作为uint64包装的4个样本框架接收的数据进行操作,需要首先解包并恢复数据的签名。然后将处理器算法子系统的输出连接到频谱和时间范围以进行可视化。分开初始化函数FPGA子系统上的各种寄存器都是用它们的默认值初始化的。

open_system (“soc\u rfsoc\u数据捕获\u过程”)

close_system (“soc\u rfsoc\u数据捕获\u过程”)

模拟

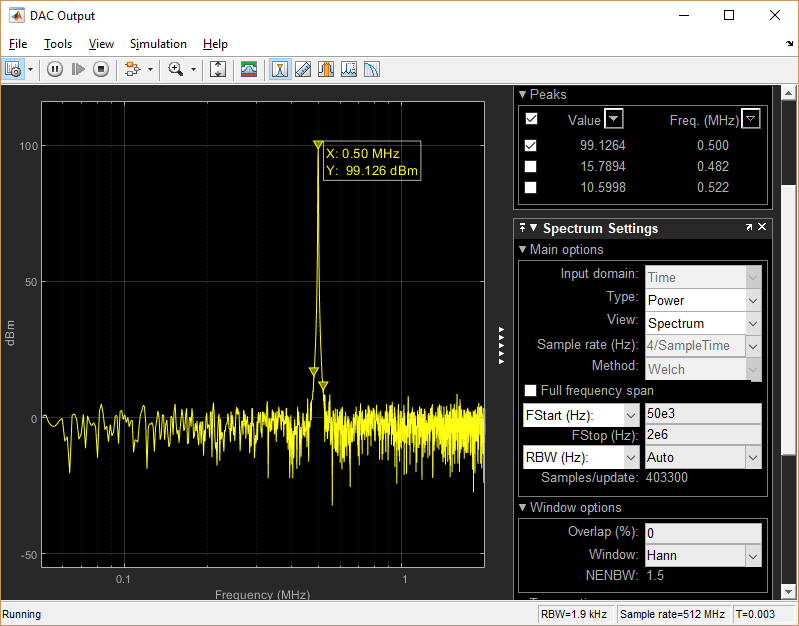

运行模型,并在频谱分析仪范围(标题为数模转换器输出.

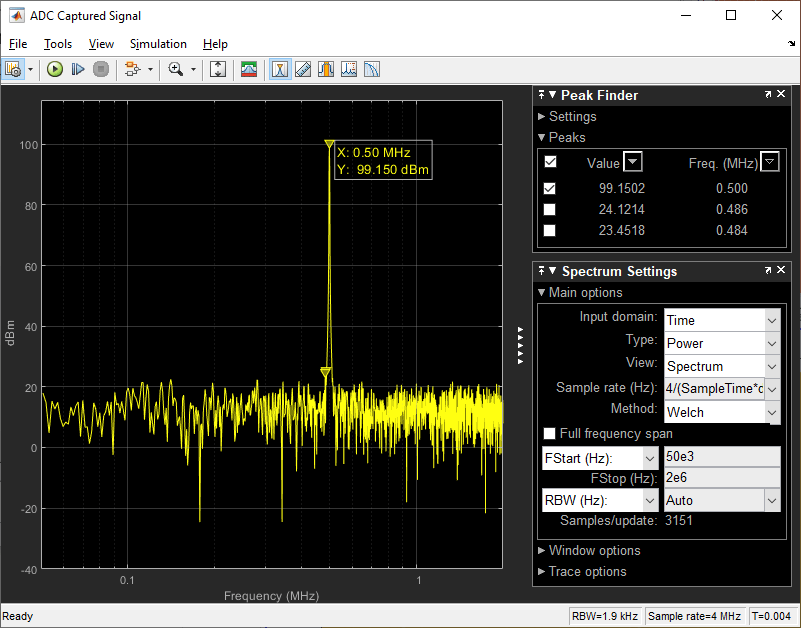

波形通过RFDC块、FPGA中的ADC捕获子系统和内存块从FPGA循环回处理器。在处理器系统中,使用名为模数转换器捕获信号.该信号还可以在时域中使用名为time scope的块来观察ADC捕获范围输出.在模拟开始后,在这些范围上观察到的数据有很大的延迟。这是因为由于长循环返回数据路径,作用域的第一帧数据的可用性存在延迟。

观察发送和接收的信号都显示0.5 MHz的音调。

修改ADC频道选择参数到5.从如下所示的命令窗口捕获第五个通道的数据。再次运行模拟,注意ADC捕获信号范围上的频谱峰值约为91.245 dBm,而通道1为100 dBm。类似地,请注意,对于信道1,时域信号的振幅从4000降低到1578。

adcChannelSelect = 5;

设计和模拟IQ模型

要在ZCU216评估套件上捕获16个通道的复杂IQ数据,请创建SoC模型soc\u rfsoc\u IQ\u数据捕获\u顶部作为顶级车型,设置硬件板选项Xilinx Zynq Ultrascale+ RFSoC ZCU216评估试剂盒.该型号包括FPGA型号soc_rfsoc_IQ_datacapture_fpga处理器模型soc\u rfsoc\u IQ\u数据捕获\u过程实例化为模型引用。按照前几节中提到的步骤,射频数据转换器配置,Haradware逻辑设计,Procesor逻辑设计通过执行以下更改。

要满足1024 MSPS的系统要求,请设置插值模式在DAC选项卡,抽取模式在模数转换器标签的RFDC块到40。设置每个时钟周期的采样在模数转换器选项卡,DAC选项卡2。这意味着流时钟频率为1024/(40*2)=12.8 MHz。设定NCO的频率至4.7 GHz及NCO的阶段所有16个频道为0。

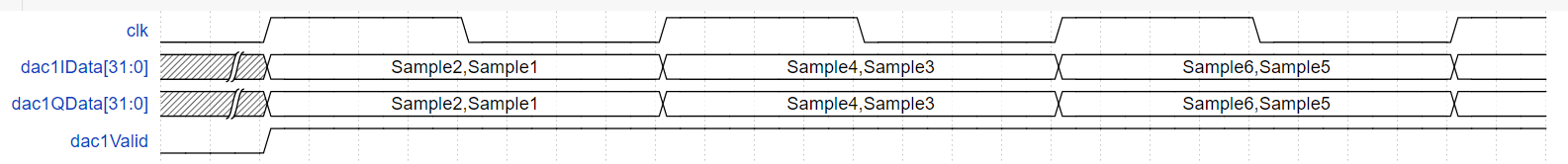

为了匹配RF数据转换器块的DAC数字接口,硬件逻辑的传输路径必须在12.8 MHz时钟的每个周期发送两个样本。此图显示RF数据转换器块的16个DAC IQ数据接口之一的数据接口。复正弦音调生成的采样率为25.6 MSPS(12.8 x 2)。

类似地,在接收端,算法必须在每个时钟周期中对2个样本进行操作。此图显示RF数据转换器块的16个ADC IQ数据接口之一的数据接口。

运行模型并在频谱分析仪上可视化ADC捕获的正弦波音调。

总结

这个例子演示了如何在Xilinx RFSoC设备上设计涉及射频数据转换器的数据路径。你们设计了一个系统,每个时钟产生多个采样的正弦波形,并配置RFDC块以更高的数字数据速率传输,真实数据为2048 MSPS, IQ数据为1024 MSPS。您还设计了数据路径,以接收传输的样本返回到设备,并通过仿真验证波形。要在硬件上验证结果,请参见使用Xilinx RFSoC设备发送和接收音调-第2部分部署. 您可以按照上述设计过程为Xilinx RFSoC设备建模任何其他高数据速率无线算法。