HW / SW Co-Design QPSK使用模拟设备传输和接收AD9361 / AD9364

此示例显示了如何在横跨臂和FPGA结构上划分的Zynq无线电平台上实现算法。QPSK发射和接收功能在硬件和软件中实现,并映射到无线电平台,如下图所示。

所需产品:下载188bet金宝搏

金宝app

通信工具箱

HDL编码器

Xilinx Zyn金宝appq的HDL编码器支持包

嵌入式编码器

金宝appSimulink编码器

用于Xilinx Zynq的嵌金宝app入式编码器支持包

基于Xilinx Zynq的广播电台的通信工具金宝app箱支持包(此包)

介绍

在该示例中,将QPSK系统的发送和接收FPGA实现组合成一个HDL IP内核并在Zynq可编程逻辑(PL)上实现。通过代码生成在Zynq ARM处理器上运行数据编码和解码。一些控制参数被添加到FPGA IP核心以显示如何使用从Simulink访问的Axi4-Lite寄存器实时调整设计。金宝app

设置

如果您还没有这样做,请确保您遵循硬件软件共同设计的安装在文档中。

硬件生成模型

硬件生成模型用于开发您希望在FPGA结构上实现的功能。HDL优化的QPSK发射器和接收器是建模的,然后在Zynq无线电平台的FPGA结构上实现。在该示例中,我们在单板上发送和接收,然而,可以通过在两个单独的板上移动发送和接收中心频率并在两个单独的板上使用相同的模型来修改该示例以在频分双工(FDD)中工作。

硬件/软件分区:通常,FPGA的可编程逻辑用于高速速率信号处理,而臂用于速度较慢,控制功能。在该示例中,在可编程逻辑上实现QPSK发送和接收物理层前端,因为它们包括诸如增益控制,滤波和频率补偿的高速率操作。数据编码和解码速度较慢,并且在臂上实现,该臂在解码消息并发送到主机以进行打印。

用于实现FPGA IP内核的IP核心生成工作流程并生成软件界面模型具有一些特定要求:

HDL子系统的端口不支持复杂的输入和输出。金宝app因此,必须在子系统边界上建模实际和虚构信号。

使用单独的数据和有效信号建模数据系统的数据输入和输出。子系统的输入和输出时钟速率必须相等,在Simulink中,必须以相同的采样率驱动数据和有效行。金宝app有效信号也必须在用户逻辑的输入和输出处进行建模。

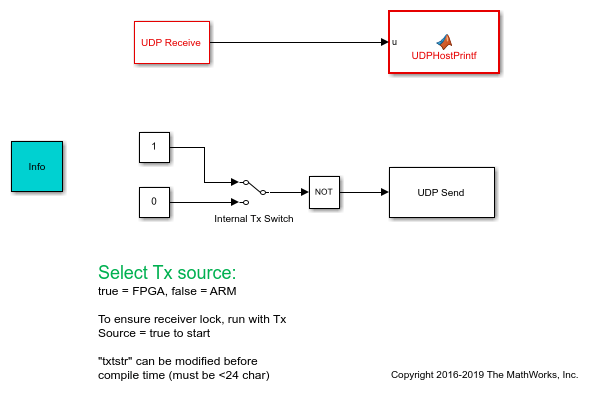

AXI4-Lite控制端口TXSRCSELECT:控制输入txsrcselect.添加以允许某种控制通过传输的数据。这txsrcselect.HDL子系统上的端口用于在两个不同的数据源之间选择发送器。如果是txsrcselect.端口为真,发送器的数据源将是存储在FPGA结构上的查找表,接收的数据应该类似于其他QPSK示例中看到的“Hello World 0xx”字符串。如果是txsrcselect.端口是假的,所接收数据的数据源将是ARM处理器,它将实时生成样本并将其发送到FPGA结构上的发射机。在这种情况下的消息将是“* Zynq HW / SW Co-Design *”。消息文本从工作区变量取出Txtstr.可以在编译时修改,以更改消息。请注意,此字符串的长度必须小于24个字符。

AXI4-Lite控制端口RXStreamEnable:控制输入rxstreambeable.添加了确保HDL算法仅在此输入为真时处理数据。这rxstreambeable.对于模拟硬件生成模型,端口总是如此。当整个设计在Zynq无线电平台的FPGA结构和ARM处理器上实现时,才会在发射机HDL算法开始发送有效数据时,该值将设置为TRUE,确保接收器正确锁定。

您可以运行此模型并确认其操作。双击交换机内部TX交换机您可以选择要从中发送哪个源。注意去和从块用于模拟天线连接并将发送用户逻辑的输出的传输数据传递给接收用户逻辑的输入。

IP核心生成工作流程

满足硬件子系统的模拟行为后,您可以启动生成HDL IP内核的过程,将其与SDR参考设计和生成软件集成,以在ARM上运行。

在准备目标时,您必须通过调用来设置Xilinx工具链hdl setuptoolpath.。例如:

>> HDLSetuptoolPath('toolname'那'Xilinx Vivado'那'工具路径'那'C:\ Xilinx \ Vivado \ 2019.1 \ Bin \ Vivado.bat');

右键单击启动目标工作流程HDL_QPSK.子系统和选择HDL代码/ HDL工作流程顾问。

在步骤1.1中,选择

IP核心生成工作流程和适当的Zynq无线电平台从选择:ADI RF SOM,ZC706和FMComms2 / 3/4,ZCU102和FMComms2 / 3/4,ZC706和FMComms5。

在步骤1.2中,选择

接收和传输路径参考设计。您可以将参考设计参数保留为默认值。

在步骤1.3中,可以使用接口表将用户逻辑信号映射到参考设计中可用的接口信号。在此示例中,我们仅使用单个通道,因此通道1连接应连接到相关端口,如下所示。

在步骤1.4中,给出了DUT合成频率,给出了系统的基带采样率的合理数量。在船舶示例中,采样率高于520ksps,因此1MHz的合成频率就足够了。

步骤2通过执行一些设计检查来准备HDL代码生成的模型。

步骤3对IP核执行实际的HDL代码生成。

步骤4将新生成的IP核心集成到较大的Zynq SDR参考设计中,生成比特流,并帮助您将其加载到电路板上。

按顺序执行每个步骤以体验完整的工作流程,或者如果您已经熟悉了准备和HDL代码生成阶段,请右键单击左侧内容表中的步骤4.1并选择跑到选定的任务。您不必修改步骤2或3中的任何默认设置。

软件生成模型和块库

在步骤4.2中,工作流生成Zynq软件生成接口模型和块库。点击

运行此任务按钮具有默认设置。

软件界面库

库包含已从HDL_QPSK子系统生成的AXI接口块。请注意,这仅暴露AXI4-Lite控件端口,而不是数据端口。数据端口存在于接收器/发射器块上,该接收器/发射器块表示FPGA用户逻辑和臂之间的数据接口。如果您在下游模型中使用库块,则在您的HDL子系统中对您的任何更新将自动传播到此库,然后在您通过工作流程时自动传播到软件生成模型。在此示例中,硬件生成模型不包含任何SDR发送或接收块,因此无法填充这些块上的参数。使用库块时,必须确保正确为应用程序配置参数。

软件界面模型

软件界面模型可以用作全SW定位的起点:外部模式仿真,循环和完全部署。请注意,每次运行步骤4.2时,将覆盖此生成的模型,因此建议在唯一的名称下保存此模型并在那里开发软件算法。已经提供了一种软件界面模型,它显示了如何决定构建此模型的方式,请参阅部分在zynq板上运行软件和硬件。

比特流生成和装载

工作流的其余部分用于生成FPGA结构的比特流并将其下载到电路板。

在步骤4.3中,工作流程顾问为FPGA结构生成位流。您可以选择通过勾选选择在外部shell中执行此步骤

在外部运行构建过程。此选择允许您在构建FPGA图像时继续使用MATLAB。在完成一些基本项目检查后,步骤将在几分钟内完成,并且该步骤将标记为绿色复选标记。但是,您必须等到外部shell显示成功的比特流构建,然后继续前进到下一步。

步骤4.4将比特流下载到设备上。在继续这一步之前,请致电

Zynq.使用以下语法功能,以确保使用无线电硬件的正确物理IP地址设置MATLAB。

>> devzynq = zynq('Linux'那'192.168.3.2'那'根'那'根'那'/ tmp');

默认情况下,无线电硬件的物理IP地址为192.168.3.2。如果在硬件设置过程中更改无线电硬件IP地址,则必须提供该地址。

或者,如果要在外部加载比特流工作流程顾问,创建一个SDR无线电对象并致电DownloadImage.在对象上的函数。

如果在步骤1.1中选择ADI RF SOM,ZC706和FMCMMS2 / 3/4,ZEDBOACK和FMCOMMS2 / 3/4或ZCU102和FMCCMS2 / 3/4无线电设备,创建了AD936X无线电对象。

>>无线电= SDRDEV('ad936x');

如果在步骤1.1中选择了ZC706和FMComms5无线电设备,请创建一个FMComms5无线电对象。

>>无线电= SDRDEV('fmcomms5');

使用无线电对象下载比特流接口所选的无线电设备。

>> DownloadImimage(收音机,'fpgaimage'那......'hdl_prj \ vivado_ip_prj \ vivado_prj.runs \ impl_1 \ system_top.bit')生成比特流的%路径

构建QPSK软件界面模型

提供了一种软件界面模型,其显示了如何修改生成的模型以将其设置为QPSK示例。此接口模型允许您运行模型监控和曲调模式或完全部署。

请注意,在软件界面模型中,AD936X发送器块将帧置于采样序列化。

设置软件模型以在ARM处理器上运行

申请模型已经在指南下设置了硬件软件共同设计工作流程, 部分配置软件界面模型。

该模型已被配置为使用基于Xilinx Zynq-7000的板目标进行以下硬件运行:ADI RF SOM Zedboard和FMComms2 / 3/4 ZC706和FMComms2 / 3/4 / 5

如果您使用的是使用ZCU102和FMComms2 / 3/4,请双击所选的硬件板目标块以更改配置以使用Xilinx Zynq UltraScale + MPSoC ZCU102 IIO无线电板目标。

该模型连续发送和接收数据,因此它已被配置为从发送中断运行。这可确保ARM和FPGA在同步中运行,并且意味着该软件将由帧速率以CHASSURY TECT驱动。

为了确保扶手处理器的有效使用,使用A用于迭代器子系统和MATLAB功能块时,通过连接50帧,发射帧大小已经增加到10000。后续速率转换块强制来自用于迭代器子系统的数据速率以匹配传输数据速率。

当运行时切换源交换机时,发射器下面尚未连接到停止块。

监控和曲调模式。这是由于所需的加工增加监控和曲调模式寄存器写入。请参阅下面使用UDP块运行模型以控制硬件的部分。

这

rxstreambeable.AXI4-Lite控制端口延迟2帧周期。这可确保发送器在接收器之前运行,以获得最强大的性能。

由于QPSK接收器通过两个操作包含一个下压,因此用户逻辑输出处的有效信号用于将有效采样率降低到时钟速率的一半。在该模型中,臂处理器的帧速率设定为采样率乘以帧大小的一半。为此相同的原因,接收器的帧大小是发射机的一半。

接收超时已设置为200

S,与帧周期相比很小。

S,与帧周期相比很小。

在zynq板上运行软件和硬件

监控和曲调模式允许您从Simulink模型中控制配置。金宝app一旦设计运行,通过切换TX开关,通过切换TX开关,从ARM或FPGA面料之间切换来自ARM或FPGA面料之间的开关。

一旦ARM已解码QPSK消息,它会使用软件界面模型中的UDP发送块将结果返回到以太网链路上的主机。UDP发送块已使用主机192.168.3.1'的默认IP地址进行配置。如果在硬件安装过程中更改了IP地址,则必须提供该地址。已经提供了一个简单的UDP接收模型,其可用于接收解码的数据并在诊断查看器中显示结果。

您还可以完全部署设计以在电路板上运行,从Simulink断开连接。金宝app在Simuli金宝appnk工具栏中,单击构建,部署和启动。在此模式下,您将无法调整参数。

使用UDP块来控制用户逻辑

监控和曲调模式需要一些开销可以包含在硬件上运行的软件中,以处理主机和电路板之间的通信。如软件界面模型所示,臂和FPGA发射器源之间的切换导致发射下部流出。已经提供了一种替代界面模型,其示出了UDP块如何用作需要更少开销的替代切换机制。

在该模型中,该开关已被UDP接收块替换,该块将能够接收UDP分组并输出源选择值。对模型进行了一些进一步的修改。

现在,发射机下溢已连接到停止块,这将导致模型在检测到下溢时退出。当硬件启动时,已经使用步进源将前十个帧周期的溢出信号栅极栅极。当发射机执行缓冲时,可以经历一些额外流动,然后在接收器稍后开始两个帧时,则再次成为。接收器初始化将导致处理器的一次性负载可能导致欠溢。

UDP接收块具有0的默认输出值0,因此逆变器已放置在UDP接收块和多路复用器之间,以确保发射机从FPGA发射源启动。在Simuli金宝appnk工具栏中,单击构建,部署和启动。一旦模型部署到硬件,UDP发射器源可用于驱动发射源选择。

提供了一个简单的UDP发射机模型,可用于在以太网链路上驱动硬件上的发射源选择。通过“收音机”192.168.3.2'的默认IP地址,已配置了发送器模型中的UDP发送块。如果在硬件安装过程中更改了IP地址,则必须提供该地址。此模型中包含UDP接收块。它可用于接收解码数据并在诊断观看者中显示结果。

此模型已被配置为为单个步骤运行,并发送包含源选择值的单个UDP数据包。将源选择到所需的源,然后单击“播放”以发送UDP控件数据包。