主要内容

硬件软件合作设计

在Xilinx上部署SDR算法的软硬件实现®Zynq®基于无线电硬件

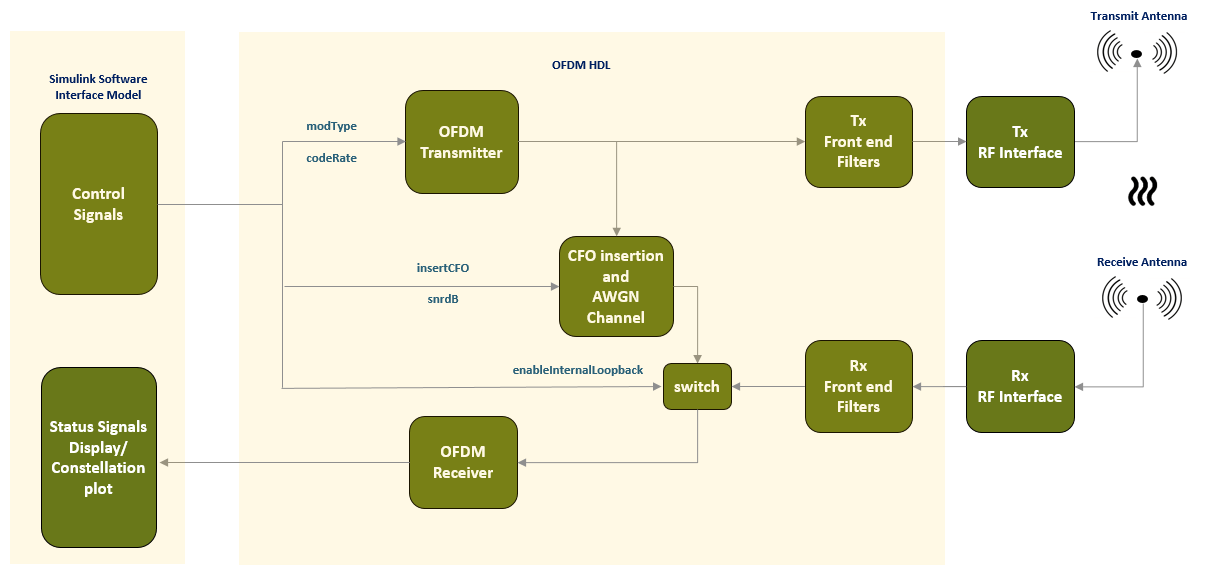

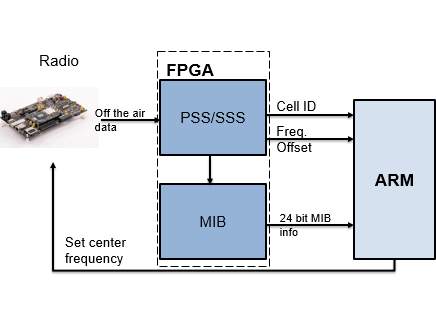

与Xilinx基于zynq的无线电通信工具箱™支持金宝app包,可以在Simulink中设计SDR算法金宝app®,然后在基于Xilinx Zynq的无线电硬件上原型设计您的设计。您可以部署在臂之间分区的硬件 - 软件(HW / SW)共设计实现®处理器和底层芯片系统(SoC)的FPGA结构,或仅针对FPGA结构的设计原型。该工作流仅在Simulink中可用。金宝app

功能

SDRDEV. |

创建用于接口的无线电对象赛灵思公司Zynq基于无线电硬件 |

downloadImage |

下载SD卡图像或位流文件 |

对象

comm.SDRDevAD936x |

与AD936x为基础的接口Zynq无线电硬件 |

comm.sdrdevfmcomms5. |

接口与FMCOMMS5Zynq无线电硬件 |

块

| AD936x接收机 | 从ad936x接收数据Zynq无线电硬件 |

| AD936x发射机 | 发送数据到ad936xZynq无线电硬件 |

| FMCOMMS5接收机 | 从FMCOMMS5接收数据Zynq无线电硬件 |

| FMCOMMS5发射机 | 发送数据到FMCOMMS5Zynq无线电硬件 |

主题

配置和部署

在此支持包中了解硬件软件共同设计功能的基础知识及其软件要求。金宝app

安装和配置硬件-软件协同设计工作流所需的额外支持包和第三方工具。金宝app

为SDR算法部署分区软硬件协同设计实现。

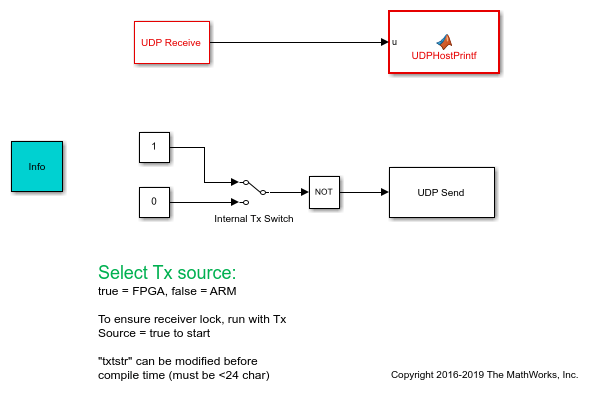

为连续和基于分组的传输和接收配置您的模型。

探索软件接口模型的ARM处理器调度器选项。

原型SDR算法仅在FPGA fabric上。

故障排除

解决在使用软硬件协同设计工作流时遇到的问题。