LTE MIB Recovery and Cell Scanner Using Analog Devices AD9361/AD9364

本示例演示如何使用模拟设备AD9361/AD9364无线前端,实现LTE主信息块(MIB)恢复系统,该恢复系统通过处理系统(PS)和Xilinx®Zynq®平台的可编程逻辑(PL)进行分区。该示例演示了如何使用HDL Workflow Advisor为PL生成HDL IP核和为PS生成嵌入式代码。该示例演示了如何在无线平台上运行该设计,以及如何重用生成的FPGA位流来构建一个LTE MIB cell scanner来检测附近的LTE cell信号。

由于硬件资源有限,该示例在ZedBoard和FMCOMMS2/3/4上不支持。金宝app

介绍

这个LTE HDL MIB恢复(无线HDL工具箱)基于Simulink®模型,金宝app可用于从LTE工具箱生成的合成数据中检测MIB信息™ 或者从空中捕获的LTE波形。

此图展示了LTE HDL MIB Recovery实例的硬件架构图。

本示例采用了来自LTE HDL MIB Reco金宝appvery示例的Simulink模型,并部署了针对软件定义无线电(SDR)的MIB接收器的软硬件协同设计实现。该示例演示了如何使用HDL Workflow Advisor为PL生成一个HDL IP核,并为PS生成嵌入式代码。该示例演示了如何在无线电平台上运行MIB接收器的设计,以及如何重用生成的FPGA位流来构建一个LTE MIB cell scanner来检测附近的LTE cell信号。

设置

要使用硬件/软件协同设计工作流,必须安装和配置其他支持包和第三方工具。有关更多信息,请参阅金宝app软硬件协同设计的安装.

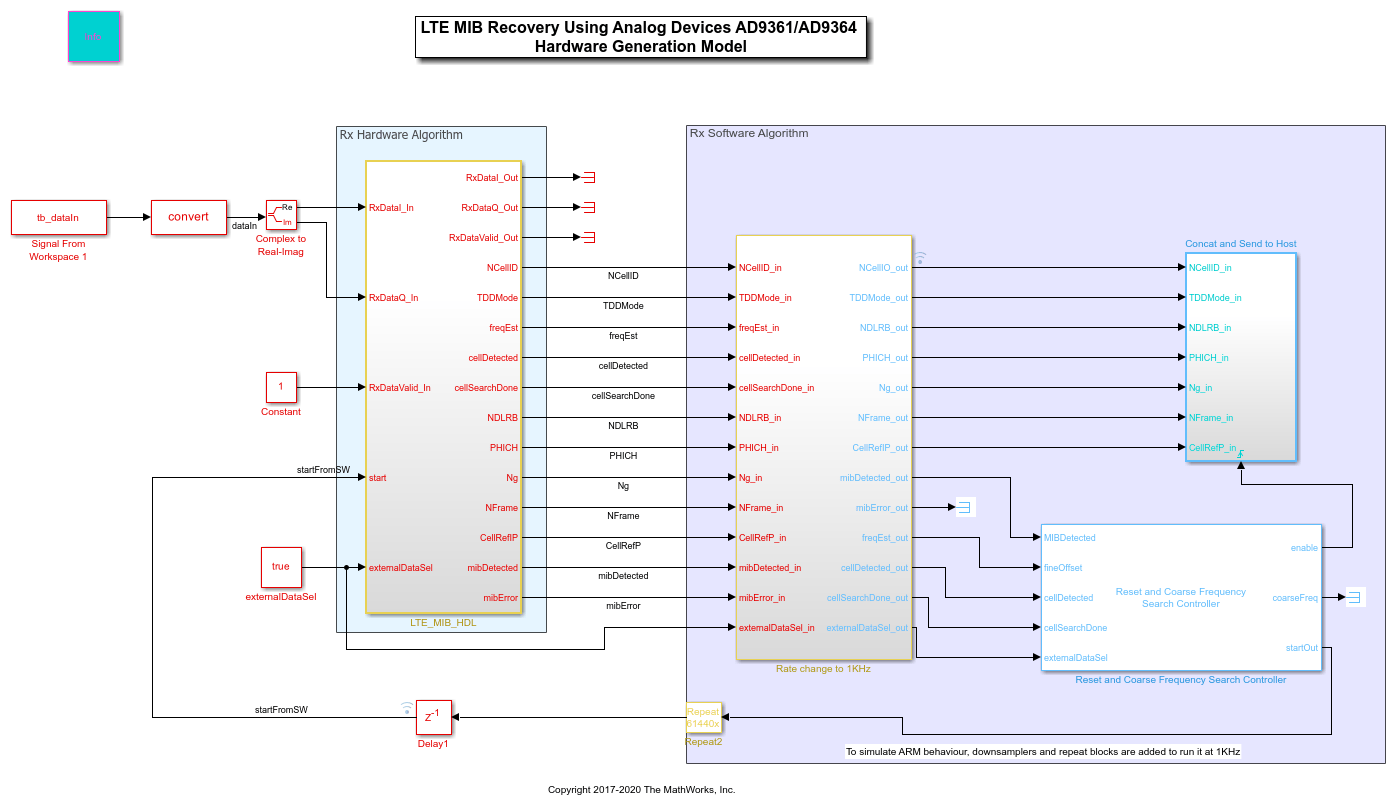

硬件生成模型

该Simu金宝applink模型是MIB恢复算法的硬件生成模型。从这个模型中,您可以为PL生成HDL代码,并使用HDL Workflow Advisor生成模板软件接口模型。使用模板软件接口模型,您可以生成一个运行在PS上的应用程序。

打开模型.

硬件/软件分区

这个LTE_MIB_HDL子系统包含在PL上实现的功能。由于设计的高速信号处理要求,大多数MIB恢复算法在PL上实现。ARM处理器从FPGA提取信息,并将有用信息发送回主机,以便通过UDP链路显示。

这个LTE_MIB_HDL子系统以软件的形式被要在ARM处理器上实现的功能所包围。这些功能包括:

修正任何粗频偏

HDL IP的启动和复位控制

将解码后的MIB信息发送给主机显示。

控制使用哪个输入数据:存储在FPGA上的现成的或预生成的测试数据。

为了在硬件上模拟软件的执行,将子系统的输出数据下采样1000。

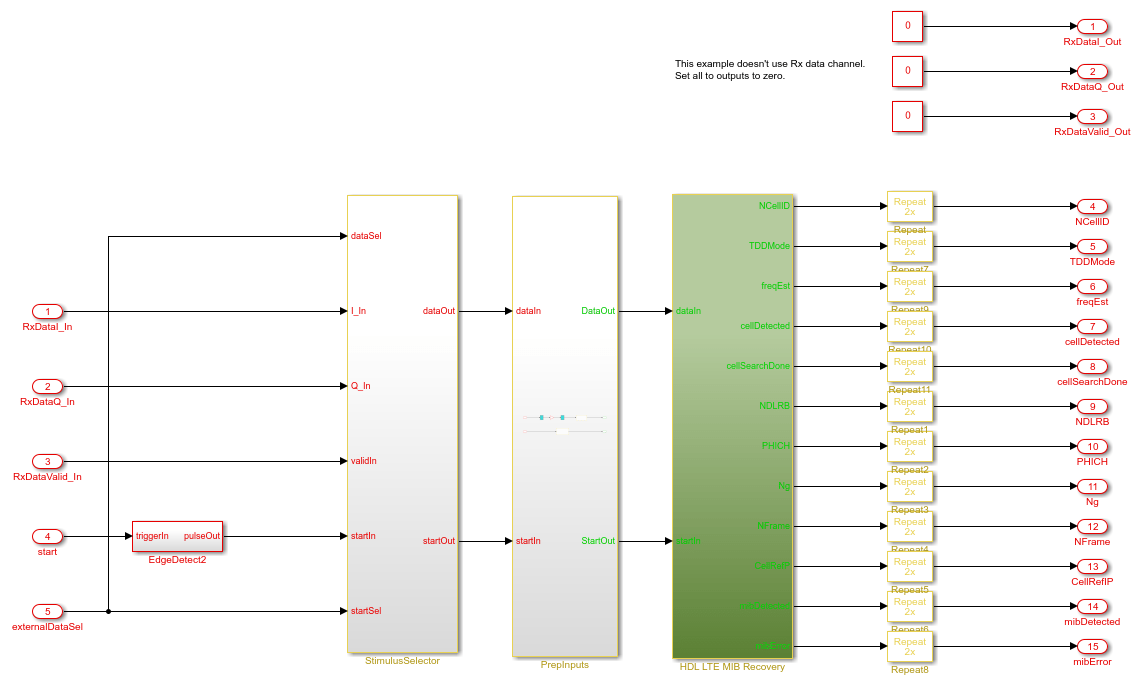

LTE_MIB_HDL子系统

这个LTE_MIB_HDL子系统采用LTE小区搜索和MIB恢复模型LTE HDL MIB恢复(无线HDL工具箱)示例,并添加额外的功能,将模型与Zynq硬件架构集成。

这个图显示了HDL LTE MIB恢复子系统从LTE HDL MIB恢复(无线HDL工具箱)的例子。有关这个子系统的更多细节,请参阅示例中的HDL优化LTE MIB Recovery一节。

这个StimulusSelector通过在非空气波形或测试数据之间切换,选择MIB恢复算法的输入数据。测试数据使用LTE工具箱预生成,并存储在FPGA上的查找表中。

这个预输入子系统调整接收数据的速率和格式。从AD9361/AD9364射频芯片的ADC接收到的数据是一个12位的值,符号扩展到16位。要使用完整的量程StimulusSelector子系统将数据样本扩展到16位StimulusSelector子系统还配置数据速率。输入数据速率为61.44 MHz,要求的最大数据速率为30.72 MHz。这种差异转化为超频因子 .因此,StimulusSelector子系统对数据进行抽样,抽样倍数为2。一个冷杉大量毁灭块实现了一个低通抽取滤波器,该滤波器捕获接收的LTE波形的中心部分,并向下采样数据到30.72 MHz。

.因此,StimulusSelector子系统对数据进行抽样,抽样倍数为2。一个冷杉大量毁灭块实现了一个低通抽取滤波器,该滤波器捕获接收的LTE波形的中心部分,并向下采样数据到30.72 MHz。

模拟硬件生成模型

要确认它的运行,你可以使用存储在LTE波形的硬件生成模型zynqRadioLTETransmitData.mat文件。这个zynqRadioHWSWLTEMIBDetectorInit初始化脚本配置模型中使用的波形。由于模型包含大量HDL优化块,需要使用基于采样的信号进行模拟,因此模拟可能需要一段时间。一旦MIB被解码,示例将显示解码的信息。

要使用从查找表(LUT)传输的内部测试数据,请设置externalDataSel阻止为false。在这种情况下,模型在内部驱动启动信号,每4s重置一次MIB恢复。

要选择存储在测试向量中的预捕获的现成数据,请设置externalDataSel阻止为true。

一旦您对硬件子系统的仿真行为感到满意,就可以开始生成HDL IP Core,将其与SDR参考设计集成,并为ARM处理器生成软件。

生成IP核心

在准备目标时,必须通过调用hdlsetuptoolpath函数。例如:

>>刀具轨迹(“ToolName”,“Xilinx Vivado”,“路径”,“C: \ Xilinx \ Vivado \ 2019.1 \ bin \ vivado.bat ');

启动目标工作流通过右键单击LTE_MIB_HDL子系统和选择HDL代码>HDL工作流顾问.

在步骤1.1中,选择

IP核心代工作流程和相应的Zynq无线电平台:ADI射频SOM,ZC706和FMCOMMS2/3/4,ZCU102和FMCOMMS2/3/4或ZC706和FMCOMMS5.由于硬件资源有限,本例不支持ZedBoard和FMCOMMS2/3/4。金宝app在步骤1.2中选择接收路径参考设计。对于本例,您可以使用默认的参考设计参数。

在步骤1.3中,接口表将DUT信号映射到参考设计中可用的接口信号。因为本示例使用单个通道,所以配置通道1连接和axis注册接口,如这些图像所示。

步骤1.4设置DUT合成频率。DUT合成频率取决于系统的基带采样率。对于本例,可以使用默认的采样率值61.44 MHz。

步骤2通过执行设计检查为HDL代码生成准备模型。

步骤3为IP核心生成HDL代码。

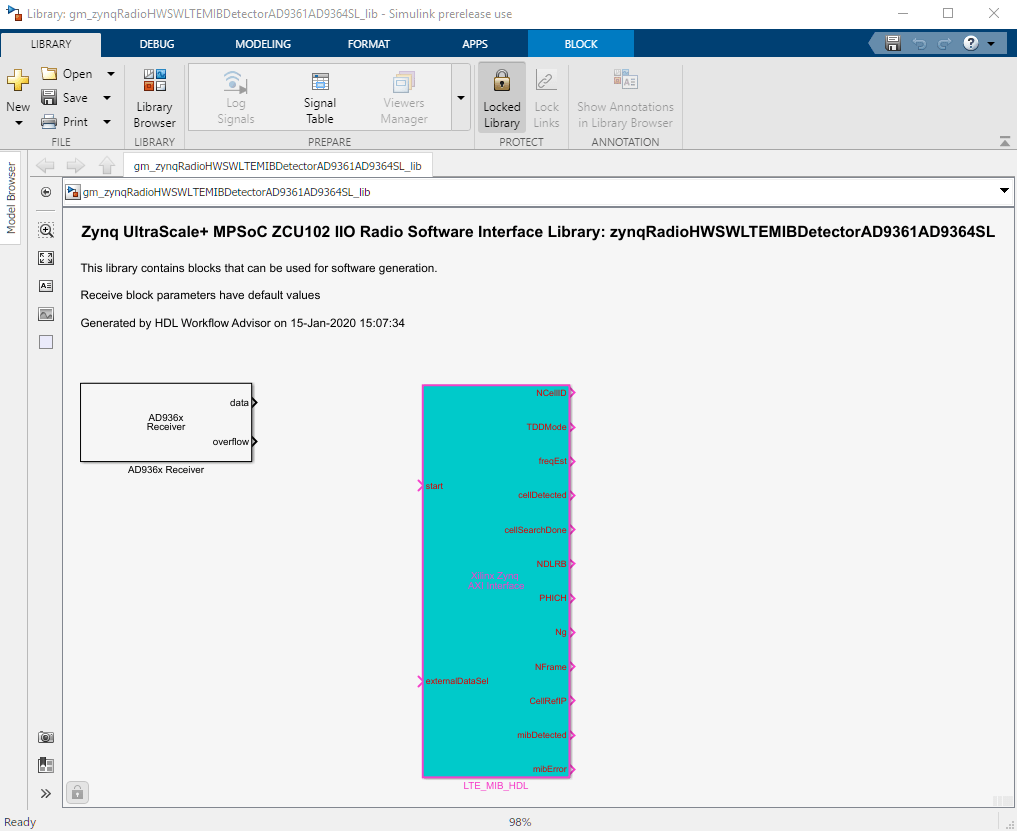

生成软件接口模型和块库

HDL Workflow Advisor的第4步将新生成的IP核集成到Zynq SDR参考设计中,生成相应的位流,并将位流加载到板上。

步骤4.2生成软件接口库和模板软件接口模型。

软件界面库

该库包含从LTE_MIB_HDL子系统生成的AXI Interface块和一个AD936x Receiver块。接收模块的数据端口表示FPGA用户逻辑与ARM处理器之间的流数据接口。由于硬件生成模型不包含任何SDR接收机块,因此AD936x接收机块参数设置为默认值。

在模型中使用库块时,必须为应用程序正确配置参数。请注意,当您再次运行步骤4.2时,对LTE_MIB_HDL子系统的任何更新都会自动传播到模型中的库块。

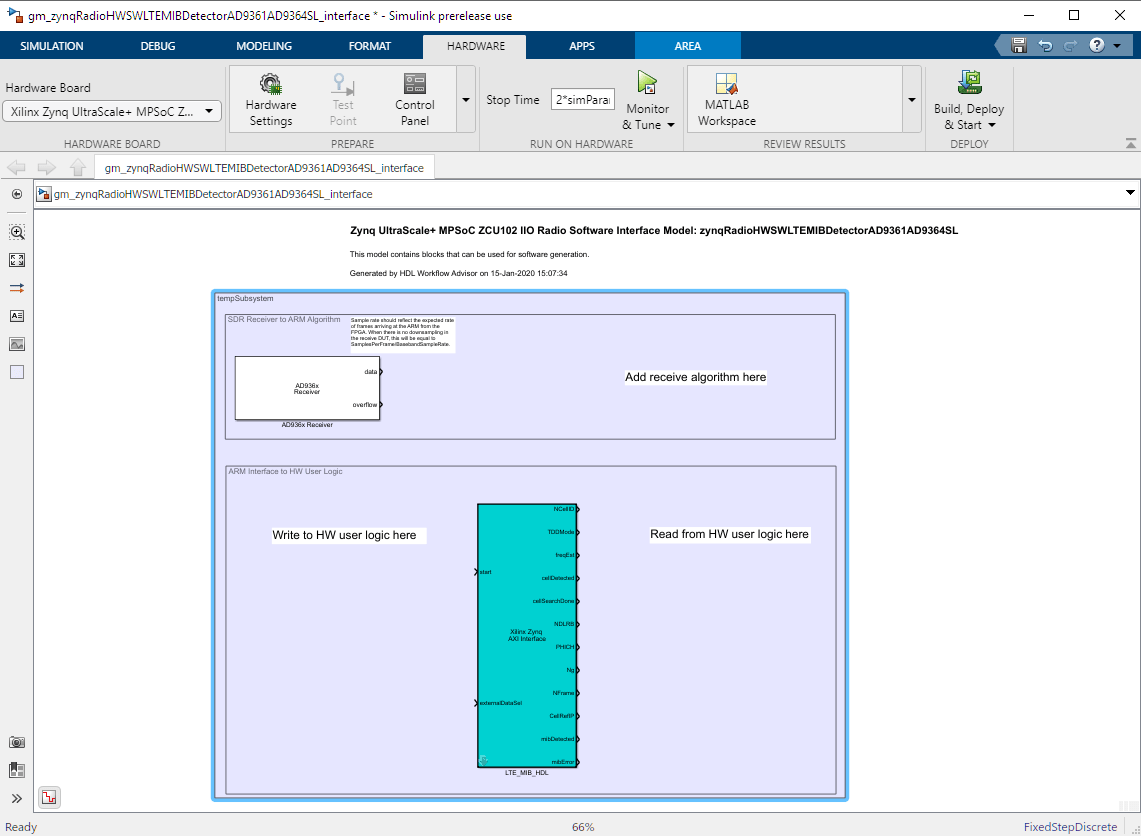

模板软件接口模型

您可以使用生成的模板软件接口模型作为一个完整的SW目标的起点,例如外部模式模拟、环中处理器和全面部署。因为每次运行步骤4.2时生成的模型都会被覆盖,所以建议将该模型保存在一个唯一的名称下,并在那里开发软件算法。

生成和加载比特流

HDL Workflow Advisor的最后步骤为PL生成一个位流,并将该位流下载到主板上。

步骤4.3为PL生成位流。您可以通过选择在外部运行构建流程.此选择允许您在构建FPGA图像时继续使用MATLAB。一旦完成了一些基本的项目检查,步骤4.3将被标记为绿色复选标记。但是,必须等到外部shell显示成功的位流构建后,才能继续下一步。

步骤4.4下载比特流到设备。在继续执行此步骤之前,请确保用无线电硬件的正确物理IP地址设置了MATLAB,方法是调用

zynq函数。

>> devzynq = zynq(“linux”,“192.168.3.2”,“根”,“根”,“/ tmp”);

默认情况下,无线电硬件的物理IP地址为192.168.3.2。如果在硬件设置过程中更改无线电硬件IP地址,则必须提供该地址。

或者,如果你想在外部加载比特流工作流的顾问,创建SDR无线电对象并使用downloadImage函数。要创建的无线电对象依赖于步骤1.1中选择的无线电平台。

如果所选的电台平台是

ADI射频SOMZ,ZC706和FMCOMMS2/3/4或ZCU102和FMCOMMS2/3/4,创建一个AD936x无线电对象。

> radio = sdrdev(“AD936x”);

如果选择的电台平台是

ZC706和FMCOMMS5,创建一个FMCOMMS5无线电对象。

> radio = sdrdev(“FMCOMMS5”);

使用与所选无线电设备接口的无线电对象下载位流。

> > downloadImage(广播,“FPGAImage”,...“hdl_prj \ vivado_ip_prj \ vivado_prj.runs \ impl_1 \ system_top.bit ')%生成的位流的路径

LTE MIB恢复软件接口模型

LTE MIB恢复模型是根据生成的模板软件接口模型开发的。该模型尝试以指定的中心频率检测单元并解码MIB。这个复位和粗频搜索控制器块校正频率偏移高达22.5 kHz通过步进通过电位偏移。当找到一个最优的步长时,搜索停止,这导致MIB解码与最小的校正精细频率偏移。这个重启控制器block在MIB检测或检测超时时重置HDL IP中的cell搜索和MIB解码。这个重启控制器Block也与粗频搜索控制器并在MIB解码前对中心频率进行校准。当使用内部测试数据运行时,将使用更简单的状态机,因为没有频率偏移。

打开模型.

模型被配置为Xilinx Zynq-7000基于董事会目标。可以将此目标用于ADI射频SOM,ZC706和FMCOMMS2/3/4或ZCU102和FMCOMMS2/3/4广播平台。为ZCU102和FMCOMMS2/3/4无线电平台,您必须通过选择Zynq UltraScale+ MPSoC ZCU102 IIO Radio在模型设置(Ctrl+E) >硬件实现>硬件板. 也可以通过双击选定的硬件板目标块来执行此操作。

在Zynq Board上运行设计

您可以在中运行LTE MIB恢复软件接口模型监视和调谐模式。在此模式下,您可以从Simulink模型控制配置。金宝app或者,要将设计部署到与Simulink断开连接的单板上,请单击金宝app构建部署和启动.

设置LTE MIB检测的源:

要使用存储在FPGA上的波形,将输入设置为

externalDataSel块为0。若要检测实时关闭空气信号,请将输入设置为

externalDataSel块1。此选项需要您所在地区的LTE基站的传输中心频率。本示例的默认中心频率是806 MHz。

软件算法被配置为在超时时重置接收器,默认值为1000,对应1秒。硬件启动信号被配置为每4秒复位接收。

主机接口模型

ARM使用UDP发送块通过以太网链路将解码的MIB信息直接发送回主机。UDP发送块的IP地址必须是主机的IP地址,默认为“192.168.3.1”。如果在硬件设置过程中更改了IP地址,则应提供该地址。

该接口模型运行在主机上,接收Zynq Radio发送的UDP数据,解包并使用scope块实时显示数据。下面的UDP接收模型演示了如何接收解码后的数据,并显示结果。

当成功运行时,示例显示从测试波形接收到的数据在FPGA上。

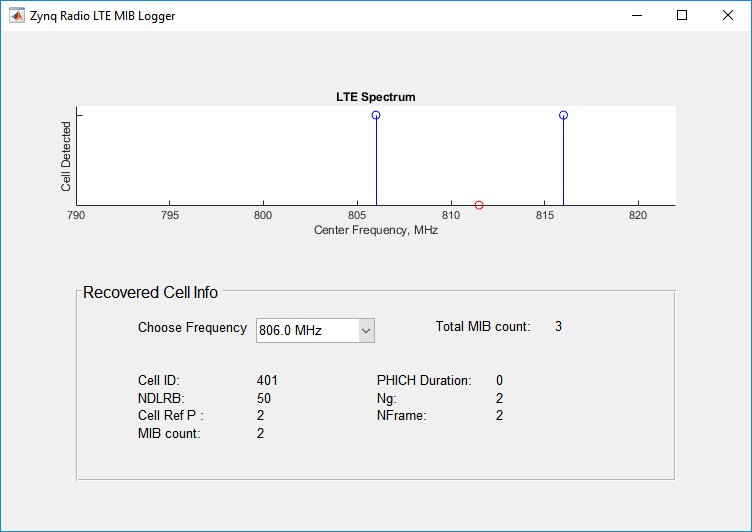

LTE MIB Cell Scanner SW接口模型

使用硬件生成模型,还可以实现LTE MIB单元扫描仪。要跨中心频率扫描并搜索本地附近的LTE基站,可以重用为MIB检测器示例生成的FPGA比特流。您只需通过随时间更新中心频率来修改LTE MIB恢复软件接口模型,并检查有效的MIB信号,如LTE MIB小区扫描仪模型所示。您还可以在中运行此模型监视和调谐模式或完全部署在单板上的模型。

打开模型.

AXI Interface块读写MIB检测器IP核上的寄存器。ARM-FPGA接口模块负责配置射频参数。你可以通过软件算法实时调整中心频率。要选择扫描的频带,请在LTE小区扫描仪和粗略频率搜索控制器块

这个LTE小区扫描仪和粗略频率搜索控制器块使用MATLAB状态机。状态机对中心频率进行编程,给射频卡设定时间,并等待有效的MIB信号。这个裸体port决定每个中心频率上的MIB检测数量。

这个连接和发送到主机block通过UDP将MIB信息和相关数据包发送到主机。为了使主机显示模型能够定期更新其状态,块还会定期向主机发送当前中心频率。

要查看解码的MIB信息,请打开LTE MIB记录器主机模型。该模型显示MIB信息和当前扫描的中心频率。

总结

这个例子展示了如何使用相同的硬件生成模型实现一个LTE MIB检测器和一个LTE单元扫描器部署为HW/SW协同设计实现。生成的HDL IP核适合这两种实现。生成的软件接口模型作为一个模板,可以容纳每个算法的特定控制方面的开发。