功能验证通常在ASIC、SoC FPGA和FPGA设计项目上消耗的时间和资源最多。为了提高效率,核查小组正在采用Accellera的方法普遍的验证方法(UVM)的标准IEEE标准1800 SystemVerilog(参考:博客第6部分和博客第10部分)。

此方法背后的主要目标是通过可重用的验证组件提高验证效率。然而,手动创建和调试UVM验证组件仍然需要大量的工作(参见:博客第8部分)。

由于许多芯片设计项目都是以算法为开端的MATLAB®要么金宝app®,测试平台的开发工作可以通过在UVM验证环境中重用MATLAB代码或Simulink模型来减少。金宝app

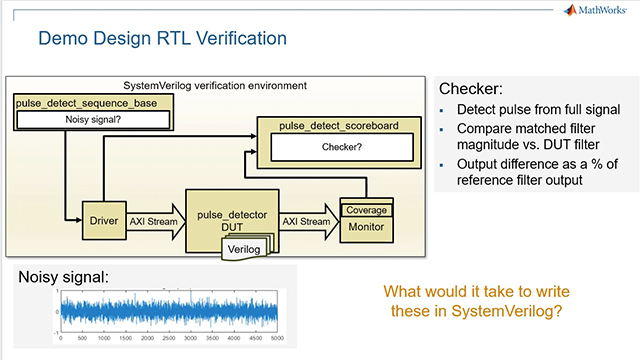

HDL Verifier™可以从MATLAB代码或Simulink模型中自动生成SystemVerilog DPI组件。金宝app此组件可以用作UVM验证记分牌中的黄金参考检查器模型,也可以用作混合信号模拟中的行为数字或模拟组件模型,或者用作UVM验证刺激中的序列项。

HDL验证器还可以直接从Simulink模型生成UVM组件。金宝appHDL验证器生成SystemVerilog UVM序列和记分板测试台模型的组件。它还为一个被测行为设计(DUT)生成SystemVerilog文件。然后,可以用手工编码的RTL或使用HDL编码器生成的RTL替换行为DUT。

生成的组件可以作为完整的UVM环境在Mentor Graphics中运行®的ModelSim®或者,®,节奏®Xcelium™或Synopsys对此®风投公司®。另外,生成的组件可以合并到现有的UVM环境中。

从Simulink模型生成UVM测试工作台或测试组件。金宝app

有关其他信息,请参见高密度脂蛋白验证器。