使用FFT HDL优化块为FPGA实现FFT

这个例子展示了如何使用FFT HDL优化块来实现硬件的FFT。

FFT和IFFT HDL优化块和系统对象支持许多应用程序的仿真和HDL代码生成。金宝app它们为不同用例提供了两种优化的架构:

流媒体基数2 ^ 2- 用于高吞吐量应用程序。使用矢量输入时,每秒(GSP)实现Gigasamples。突发的基数2- 对于低区域应用。只使用一个复杂的蝴蝶。

此示例包括两个模型,该模型分别展示了如何使用FFT HDL优化块的流和突发架构。

流拉媒体2 ^ 2架构

现代adc能够以每秒几千兆采样速率对信号进行采样。然而,最快的FPGA的时钟速度低于这个采样率。fpga通常以数百兆赫兹的频率运行。在FPGA上执行GSPS处理的一种方法是以低得多的时钟速率同时处理多个样本。许多现代fpga支持JESD204B金宝app标准接口,该接口接受GHz时钟速率的标量输入,并以较低的时钟速率产生采样向量。因此,现代信号处理需要矢量处理。

这流媒体基数2 ^ 2架构旨在支持高吞吐量用例。金宝app此示例模型使用输入向量大小为8,并使用该输入矢量大小计算FFT流媒体基数2 ^ 2体系结构。有关时序图,支持的功能和FPGA资源使用金宝app情况,请参阅FFT HDL优化块参考页面。

modelname =.'ffthdloptimizedexample_streaming';Open_System(ModelName);

InitFcn回调(模型属性>回调> InitFcn)为模型设置参数。在这个例子中,参数控制了FFT的大小和输入数据的特征。

FFTLength = 512;

输入数据是两个正弦波,200 kHz和250 kHz,每个都在1 * 2E6 Hz上采样。输入矢量尺寸为8个样本。

Framesize = 8;fs = 1 * 2e6;

为了证明数据不需要连续来,此示例适用每个其他循环的有效输入。

ValidPattern = (1,0);

打开Spectrum Viewer并运行示例模型。

Open_System('ffthdloptimizedexample_streaming / spectrum Viewer / Power Spectrum Viewer');sim(modelname);

Burst RADIX 2(最小资源)架构

使用突发的基数2具有限制FPGA资源的应用程序的架构,尤其是当FFT长度大时。该架构仅使用一个复杂的蝴蝶来计算FFT。设计接受数据准备好被断言,一旦整个FFT帧保存到内存中,就开始处理。在处理时,设计无法接受数据,因此准备好是断言。有关时序图,支持的功能和FPGA资源使用金宝app情况,请参阅FFT HDL优化块参考页面。

modelname =.'ffthdloptimizedexample_burst';Open_System(ModelName);

InitFcn回调(模型属性>回调> InitFcn)为模型设置参数。在这个例子中,参数控制了FFT的大小和输入数据的特征。

FFTLength = 512;

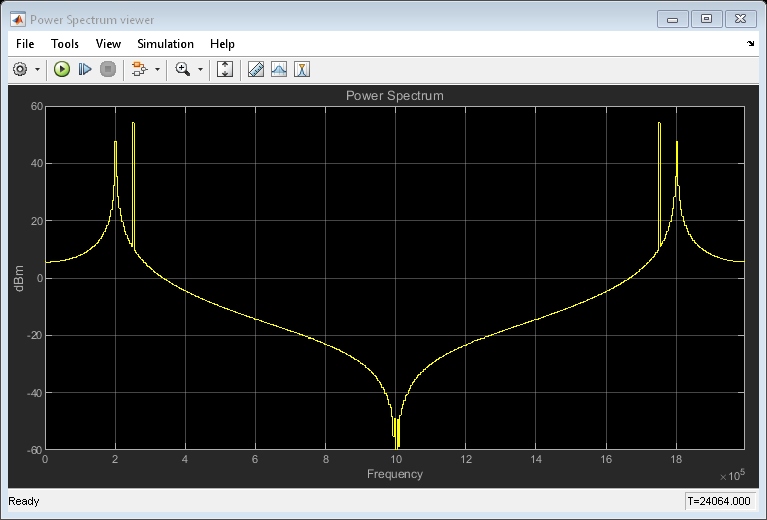

输入数据是两个正弦波,200 kHz和250 kHz,每个都在1 * 2E6 Hz上采样。数据每个周期都有效。

fs = 1 * 2e6;valtpattern = 1;

打开Spectrum Viewer并运行示例模型。

Open_System('ffthdloptimizedexample_burst / spectrum Viewer / Power Spectrum Viewer');sim(modelname);

生成HDL代码和测试台

需要HDL Coder™许可证为此示例生成HDL。

选择一个模型以生成HDL代码和测试台:

systemname ='ffthdloptimizedexample_burst / fft hdl优化爆发';

或

systemname ='ffthdloptimizedexample_streaming / fft hdl优化流';

使用此命令为FFT模式生成HDL代码。所生成的可用于任何FPGA或ASIC目标。

makehdl(systemname);

使用此命令生成测试台,该测试台与模拟模拟行为的HDL仿真结果进行比较。金宝app

makehdltb(systemname);