使用Zynq板在实时音频输入上运行音频过滤器

这个例子展示了如何建模一个音频系统,并使用音频参考设计在Zynq®板上实现它。

简介

在这个例子中,你:

用低通、带通和高通滤波器建模音频系统

在Zynq板上使用音频参考设计实现它

本例的目标是通过Zedboard或Zybo板的线输入接收音频输入,在FPGA上进行处理,并将处理后的音频传输到扬声器。上图显示了这样一个系统的高级架构。它使用音频编解码器接口到外设,并将模拟信号转换为数字信号,反之亦然。音频编解码器ip用于配置音频编解码器,以及在Zynq Soc和音频编解码器之间传输音频数据。Filter IP用于音频处理。ARM处理器用于控制滤波器的类型,即低通,带通或高通。

开始之前

要运行此示例,您必须安装并设置以下软件和硬件:

Xilinx Zyn金宝appq平台的HDL编码器支持包

Xilinx Zynq平台嵌入金宝app式编码器支持包

Xilinx Vivado 2019.1版

ZedBoard或Zybo Board

若要设置Zedboard板,请参阅设置Zynq硬件和工具章节。着眼于Xilinx Zynq平台的例子。将手机或MP3播放器的音频输入连接到行杰克和耳机或扬声器HPH出来千斤顶上Zedboard如下所示。类似的设置可以在Zybo板上完成。有关Zybo板设置,请参阅设置Zybo板章节。为Zynq工作流定义定制板和参考设计的例子。

简介

在下面的模型中,音频文件被用作DUT子系统的输入,Audio_filter.在Simulink中对该模型进行仿真,处理后的音频效果可金宝app以通过音频设备写入器块和频谱分析仪块显示过滤音频输出的频谱图。

modelname =“hdlcoder_audio_filter_biquad”;open_system (modelname);

用低通、带通和高通滤波器建模系统

滤波器系数可以使用MATLAB®函数或Simulink®生成。金宝app在这个模型中,filterDesigner工具用于为每种类型的过滤器生成过滤器系数。然后将这些滤波器系数导出并存储为MATLAB文件。这些系数将用于在Simulink中设计滤波器。金宝app在该模型中,根据相应的滤波器系数,使用Simulink中的离散IIR滤波器块作为Biquad低金宝app通、带通或高通滤波器。

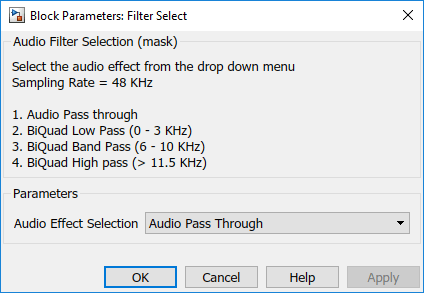

您可以通过在Simulink中模拟该模型来测试该模型。金宝app频谱分析仪上看到的频率范围和通过音频设备写入器块听到的音频效果应该根据所选滤波器的类型而有所不同。过滤器选择块用于选择要在音频输入上进行的过滤类型。

定制Zynq板的模型

为了在Zedboard上实现这个模型,你必须首先在Vivado中创建一个参考设计,它接收Zedboard上的音频输入,并将处理后的音频数据传输出Zedboard。有关如何创建集成音频滤波器模型的参考设计的详细信息,请参阅在Zynq板上编写音频系统参考设计的例子。

关于Zybo板,请参考在ZYBO板上编写音频系统参考设计.

在参考设计中,左右声道音频数据被组合在一起,形成一个单一声道。它们被连接起来,使得下24位是左信道,上24位是右信道。在上面所示的S金宝appimulink模型中,Data_in被分为2个通道,即左通道和右通道。它们的大小除以2,两个通道加在一起形成一个通道。在此通道上进行过滤。

Data_in而且Valid_in为AXI4-Stream信号。要了解如何使用AXI4-stream接口,请参阅用简化流协议建模流算法部分开始使用Zynq工作流中的AXI4-Stream接口的例子。Data_in包含要处理的音频数据和Valid_in作为使能信号。每个滤波器都映射到Zedboard或Zybo板上的LED上,以直观地指示滤波器是否打开或关闭。

FilterSelect输入通过AXI4 LITE接口控制。

使用AXI4-Stream接口生成HDL IP核

接下来,您可以启动HDL Workflow Advisor并使用Zynq硬件-软件协同设计工作流将此设计部署到Zynq硬件上。有关更详细的分步指南,可以参考着眼于Xilinx Zynq平台的例子。

1.在MATLAB命令窗口中使用以下命令设置Xilinx Vivado合成工具路径。运行该命令时,请使用自己的Vivado安装路径。

hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,“C: \ Xilinx \ Vivado \ 2019.1 \ bin \ vivado.bat ');

2.使用以下命令将IP存储库文件夹和Zedboard注册文件添加到MATLAB路径:

目录(fullfile (matlabroot,“工具箱”,“hdlcoder”,“hdlcoderdemos”,“customboards”,“ipcore”));目录(fullfile (matlabroot,“工具箱”,“hdlcoder”,“hdlcoderdemos”,“customboards”,“ZedBoard”));

对于Zybo板使用以下命令。

目录(fullfile (matlabroot,“工具箱”,“hdlcoder”,“hdlcoderdemos”,“customboards”,“ipcore”));目录(fullfile (matlabroot,“工具箱”,“hdlcoder”,“hdlcoderdemos”,“customboards”,“ZYBO”));

3.从DUT子系统启动HDL Workflow Advisor,hdlcoder_audio_filter_biquad / Audio_filter或者双击模型中的Launch HDL Workflow Advisor框。

在这个示例模型中,已经为Zedboard保存了目标界面设置,因此Task 1.1至1.3中的设置将自动加载。有关在模型中保存目标接口设置的详细信息,请参阅在模型中保存目标硬件设置的例子。

在任务1.1中IP核生成为目标工作流程,ZedBoard为目标平台.如果你使用Zybo板,然后选择ZYBO作为目标平台而不是Zedboard。

在Task 1.2中音频系统与AXI4流接口为参考设计.

AXI4-Stream接口用于在参考设计和滤波算法IP之间传输音频数据。AXI4-Stream接口包含数据(数据)和控制信号,例如数据有效(有效的)、背压(准备好了)和数据边界(TLAST).至少数据而且有效的AXI4-Stream IP核生成需要信号。在任务1.3中,使用目标平台接口表加载如下图所示。音频数据流端口,Valid_in,Data_in,Valid_out而且Data_out,映射到AXI4-Stream接口,Pass_through_LED, BiQuad_LPF_LED, BiQuad_BPF_LED,BiQuad_HPF_LED映射到Zedboard上的led和控制参数端口Filter_select映射到AXI4-Lite接口。如果您正在使用Zybo板,然后通过选择手动将led映射到过滤器led通用[0:4].

AXI4-Stream接口以主/从模式通信,主设备向从设备发送数据。因此,如果数据端口是输入端口,请将其分配给AXI4-Stream奴隶接口,如果数据端口是输出端口,则将其分配给AXI4-Stream主接口。

3.右键单击任务3.2,生成RTL代码和IP核,并选择运行到选定任务来生成IP核。您可以在生成的IP核报告中找到IP核的寄存器地址映射和其他文档。

集成IP到AXI4-Stream音频兼容参考设计

接下来,在HDL Workflow Advisor中运行嵌入式系统集成将生成的HDL IP核部署到Zynq硬件上。

1.运行任务4.1,创建项目.该任务将生成的IP核插入音频系统与AXI4流接口参考设计。如第一个图所示,这个参考设计包含了处理Zedboard进出音频数据的ip。生成的项目是一个完整的Zynq设计,包括算法部分(生成的DUT算法IP)和平台部分(参考设计)。有关如何创建集成音频滤波器模型的参考设计的详细信息,请参阅在Zynq板上编写音频系统参考设计或在ZYBO板上编写音频系统参考设计的例子。

2.单击Result窗格中的链接,打开生成的Vivado项目。在Vivado工具中,单击开放式体块设计查看Zynq设计框图,其中包括生成的HDL IP核、其他音频处理IP和Zynq处理器。

3.在HDL Workflow Advisor中,运行其余任务以生成软件接口模型,并构建和下载FPGA比特流。选择下载任务中的编程方法程序目标设备将FPGA比特流下载到Zynq板上的SD卡上,这样当您为Zynq板上电循环时,您的设计将自动重新加载。

生成ARM可执行文件以优化FPGA Fabric上的参数

在任务4.2中生成软件接口模型,生成软件接口模型.

1.在你从软件接口模型生成代码之前,注释掉音频输入源和音频输出接收器,即来自多媒体文件,数据类型转换,缓冲区,音频设备写入器和频谱分析仪块。这些块不需要在ARM处理器上运行。Audio_filter IP在FPGA fabric上运行为*Filtering_Algorithm”。ARM处理器使用AXI4-Lite接口来选择滤波器类型,即双方低通、带通、高通或直通。

在生成的模型中,单击Hardware窗格并转到硬件设置打开配置参数对话框。

选择解算器并将“停止时间”设置为“inf”,单击“确定”。

在Hardware窗格中,单击监视和调优按钮。

单击运行按钮。Embedded Coder构建模型,下载ARM可执行文件到Zynq板硬件,执行它,并将模型连接到运行在Zynq板硬件上的可执行文件。

中的下拉选项可选择要使用的过滤器类型过滤器选择块

滤过的音频输出可以通过插入耳机或扬声器听到HPH出来Zynq董事会上的jack。根据所选的滤波器,Zynq板上相应的LED会亮起。在本例中,当选择直通(不使用滤波器)选项时,LD0打开,当选择双方低通滤波器时,LD1打开,当选择双方带通滤波器时,LD2打开,当选择双方高通滤波器时,LD3打开。