主要内容

IP核心生成的Speedgoat Simulink可编程I/O模块的工作流程金宝app

HDL CODER™使用IP核心生成工作流基础架构生成可重复使用的HDL IP核心,用于Speedgoat Simulink-simulink可编程I/O模块,该模块支持xilinx金宝app金宝app®Vivado®。工作流产生了IP核心报告,该报告显示目标接口配置和您指定的代码生成器设置。您可以通过将其添加到嵌入式系统集成环境中,将IP核心集成到较大的设计中。看自定义IP核心生成。

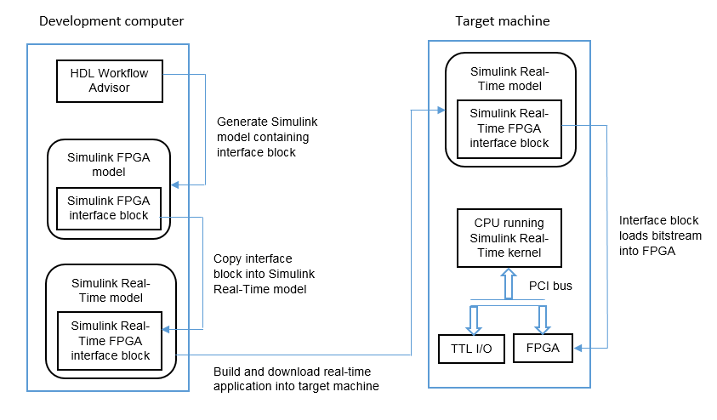

该图显示了该软件如何使用AXI接口生成IP核心,并将IP核心集成到FPGA参考设计中。

金宝app支持的I/O模块

了解HDL编码器支持的I/O模块金宝app金宝appSimulink实时FPGA I/O工作流程,请参阅Speedgoat FPGA支金宝app持HDL Workflow Advisor。

IP核心生成工作流程

此工作流具有以下关键功能:

使用Xilinx Vivado作为合成工具。

生成可重复使用的可共享的IP核心。IP核心软件包将RTL代码,C标头文件和IP Core定义文件。

创建一个将IP核心集成到Speedgoat参考设计中的项目。

生成FPGA bitstream,并将bitstream下载到目标硬件。

构建FPGA bitstream后,工作流生成一个金宝app®实时™模型。该模型是一个接口子系统模型,该模型包含用于编程FPGA并在实时执行期间通过PCIE总线与I/O模块通信的块。

限制

IP核心生成工作流不支持:金宝app

RAM架构设置

通用的RAM没有时钟启用。使用不同的时钟用于IP核心和AXI接口。这

ipcore_clk和Axilite_aclk必须同步并连接到同一时钟源。这ipcore_resetn和Axilite_aresetn必须连接到同一重置源。看全局重置信号与IP核心时钟域的同步。