HDL测试台特性

生成和定制HDL测试台

使用HDL测试台属性,您可以启用并自定义测试台生成。

将这些属性指定为名称 - 值参数generatehdl函数。名称属性名称和价值是相应的价值。您可以以任何顺序指定多个名称值参数'name1',value1,...,'namen',valuen.

例如:

fir = dsp.firfilter(“结构”,直接形成反对称的);generatehdl(杉木、'inputDatatype'15) numerictype(16日,......“GenerateHDLTestBench”,“上”,'multifiletestbench',“上”);

一般的

GenerateHDLTestBench- - - - - -生成HDL测试台

'离开'(默认)|“上”

为HDL过滤器代码生成HDL测试台,指定为'离开'或“上”.试验台将生成的输入刺激应用于生成的滤波器代码,并将输出与存储的MATLAB进行比较®仿真结果。

testbenchname.- - - - - -生成的测试台的文件名

filtername_TB.

filtername_TB.生成的测试台的文件名,指定为filtername_TB.filtername是生成的VHDL实体或Verilog模块的名称。属性,可以自定义此名称名称财产。该编码器将文件类型扩展名添加到测试台名称,如下所示VerilogFileExtension或vhdlfileextension.属性。控件指定的文件夹中有测试工作台文件targetDirectory.财产。

如果指定的值在目标语言中是保留字,则编码器会添加后缀_rsvd这个值。属性更新后缀值保留wordpostfix.财产。更多信息请参见解决HDL保留词冲突.

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

errormargin.- - - - - -测试台阶比较的误差余量

4(默认)|正整数

测试台阶比较的误差余量,指定为4或正整数。测试台将结果与参考信号进行比较。以下HDL优化可以生成测试台基代码,该代码产生与原始过滤器功能产生的结果不同的数字结果:

FIRAdderStyle设置为“树”或'管道'addpipelineregisters.使用FIR,不对称的FIR和对称FIR滤波器

错误余量指定可接受的最小位数,在测试台面发出警告之前,数字结果可能会有所不同。

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

MultifileTestBench- - - - - -生成多文件测试台

'离开'(默认)|“上”

生成多文件测试台,指定为'离开'或“上”.当此属性设置为时“上”,编码器为测试台代码、辅助函数和测试台数据生成单独的文件,而不是单个文件。文件名派生自testbenchname.和TestBenchDataPostfix属性。例如,如果生成的VHDL实体或Verilog模块的名称是my_fir_filt.,测试台的默认文件名是:

my_fir_filt_tb- 测试台代码my_fir_filt_tb_pkg.-助手功能包my_fir_filt_tb_data.-测试矢量数据包

控件定义的文件类型扩展名附加到这些文件名之后VerilogFileExtension或vhdlfileextension.属性。

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

TestBenchDataPostfix- - - - - -后缀为测试台数据的文件名

“_data”(默认)|字符向量|字符串标量

postfix到文件名称的文件名,指定为“_data”,一个字符向量,或字符串标量。代码生成一个测试台数据文件,该文件的文件名是通过将该后缀附加到testbenchname.属性值。

依赖性

此属性仅适用于GenerateHDLTestBench和MultifileTestBench属性设置为“上”.

testbenchrewesspostfix.- - - - - -后缀引用信号名称

“_ref”(默认)|字符向量|字符串标量

postfix参考信号名称,指定为“_ref”,一个字符向量,或字符串标量。编码器将此后缀应用于测试台中的参考输出信号。编码器将参考信号数据表示为数组。

filter_out_expected: filter_in_data_log_type:= (-2.4228738523269194E-03, -2.0832449820793104E-03, 6.7703446401186345E-03,…

SIGNAL filter_out_ref: real:= 0.0;——双…filter_out_ref < = filter_out_expected (TO_INTEGER (filter_out_addr));

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

时钟和重置

钟声- - - - - -测试台在NS中的测试台驱动时钟输入信号高(1)

5(默认)|积极的标量

试验台驱动高(1)ns的时钟输入信号的周期,指定为5或者是一个正标量。可以指定整数或双精度浮点值,小数点后的有效位数最多为6位。

依赖性

此属性仅适用于GenerateHDLTestBench和ForceClock属性设置为“上”.

ClockLowTime- - - - - -试验台驱动时钟输入信号低(0)ns的周期

5(默认)|积极的标量

试验台驱动低(0)ns的时钟输入信号的周期,指定为5或者是一个正标量。可以指定整数或双精度浮点值,小数点后的有效位数最多为6位。

依赖性

此属性仅适用于GenerateHDLTestBench和ForceClock属性设置为“上”.

ForceClock- - - - - -测试台力强制时钟输入信号

“上”(默认)|'离开'

测试台力强制时钟输入信号,指定为以下之一:

“上”- 测试台力强制时钟输入信号。的价值观钟声和ClockLowTime属性控制时钟波形。'离开'-必须从外部源驱动时钟输入信号。

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

ForceClockEnable- - - - - -试验台强制时钟使能输入信号

“上”(默认)|'离开'

试验台强制时钟使能输入信号,指定为以下之一:

“上”-测试台强制时钟使能输入信号。极性高(1)。此信号也服从HoldTime财产。'离开'- 您必须驱动时钟从外部源启用输入信号。

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

TestBenchClockEnableDelay- - - - - -从确定复位到确定时钟使能之间的时钟周期

1(默认)|正整数

从确定复位到确定时钟使能之间的时钟周期,指定为1或正整数。测试台等待在DEASERINGSERTION复位信号之间进行此循环并断言时钟使能信号。的HoldTime财产也适用。

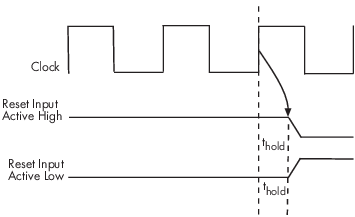

在图中,试验台在标记的间隔后取消一个高活动复位信号保持时间.然后,测试台在一个进一步的间隔(标记)后断言时钟启用时钟使延迟.

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

Forcereset.- - - - - -测试台强制复位输入信号

“上”(默认)|'离开'

试验台强制复位输入信号,指定为以下其中之一:

“上”—试验台强制复位输入信号。属性指定保持时间来控制重置时间HoldTime财产。'离开'-你必须驱动复位输入信号从外部来源。

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

HoldTime- - - - - -保持输入数据值和ns中的强制重置信号

2(默认)|积极的标量

按住输入数据值的保持时间,并指定为NS中的强制重置信号2或者是一个正标量。测试台保持过滤器数据输入信号和强制复位输入信号的指定时间间隔超过上升的时钟边缘。可以指定整数或双精度浮点值,小数点后的有效位数最多为6位。

下图显示了保持时间的应用t持有,用于复位和数据输入信号。信号被强制分为高电平和低电平。的ResetLength属性设置为2个周期,并且试验台将重置信号断言为总共2个周期加上t持有.

保持时间复位输入信号

保持数据输入信号的时间

依赖性

此属性仅适用于GenerateHDLTestBench和Forcereset.属性设置为“上”.

ResetLength- - - - - -测试台支线断言复位信号的时钟周期数

2(默认)|正整数

holdinputdatabetweensamples.- - - - - -试验台将超时钟滤波器的输入数据保存在有效状态

'离开'(默认)|“上”

测试台在有效状态下保持过时的过滤器的输入数据,指定为'离开'或“上”.串行体系结构和分布式算法体系结构实现内部时钟速率高于输入速率。在这样的过滤器实现中,运行的是基本时钟N循环(n> = 2),用于每个输入样例。此属性与测试台将输入数据保存在有效状态的时钟周期数有关。

'离开'- 测试台在一个时钟周期中以有效状态保持数据值。下一个N-1周期,数据处于未知状态(表示为“X”).强制输入数据处于未知状态将验证生成的筛选器代码仅在第一个周期注册输入数据。“上”- 测试台在跨越有效状态下保持输入数据值N时钟周期。

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

InitializeTestBenchInputs- - - - - -初始化试验台输入

'离开'(默认)|“上”

初始化测试台输入,指定为以下之一:

'离开'-在模拟开始时,试验台驱动一个未知状态(表示为“X”)到输入端口。“上”-在模拟开始时,试验台将0驱动到输入端口。

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

刺激措施

Testbenchstumulus.- - - - - -输入刺激应用于生成的过滤器

{'冲动','踩','ramp','chirp','噪音'}(默认)|字符向量的单元格阵列|字符串数组

输入刺激应用于生成的过滤器,指定为{'冲动','踩','ramp','chirp','噪音'},字符向量或字符串阵列的小区阵列。单元格或字符串阵列必须是默认刺激集的子集。您可以在任何顺序中指定刺激的组合。例如:

generatehdl(filt,'inputDatatype'15) numerictype(16日,......'generatehdltestbench',“上”,......“TestBenchStimulus”, {'斜坡','冲动','噪音'})

testbenchusertumulus.财产。什么时候testbenchusertumulus.是一个非空的矢量,优先考虑Testbenchstumulus..

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

testbenchusertumulus.- - - - - -自定义输入刺激

[](空向量)(默认)|输入数据矢量

自定义输入刺激,指定为以下之一:

[](空向量)-试验台使用Testbenchstumulus.属性生成输入数据。输入数据矢量 - 测试台将此输入刺激应用于生成的滤波器。您可以将向量指定为返回向量的函数调用。

例如,该函数调用产生一个平方波,样本频率为每秒8位(FS / 8)。

调用时指定此刺激Repmat ([1 1 1 10 0 0 0],1,10)

generatehdl.generatehdl(filt,'inputDatatype'15) numerictype(16日,......'generatehdltestbench',“上”,......“TestBenchUserStimulus”,repmat([1 1 1 10 0 0 0],1,10))

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

TestBenchCoeffStimulus- - - - - -FIR或IIR滤波器的系数刺激

[](空向量)(默认)|系数矢量(仅限冷杉过滤器)|系数和刻度值的单元数组(仅IIR滤波器)

FIR或IIR过滤器的系数刺激,指定为以下之一:

[](空向量) - 测试台使用过滤器对象系数并强制输入刺激。该序列显示对输入刺激的响应,并验证接口根据预期将一组系数写入系数存储器。系数向量(仅FIR滤波器)-滤波器处理输入刺激两次:一次与滤波器对象系数和一次与系数刺激。试验台验证接口将两组不同的系数写入系数存储器。更多信息请参见生成可编程FIR系数测试台.

单元数和尺度值的单元格阵列(仅限IIR过滤器) - 将刺激指定为刻度值的列向量和二阶部分(SOS)矩阵。滤波器处理两次输入刺激:一次用滤波器对象系数一次,一次用系数刺激一次。试验台验证接口将两组不同的系数写入系数存储器。更多信息请参见生成可编程IIR系数试验台.

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”和CoefficientSource属性设置为'processOrinterface'.

TestBenchFracDelayStimulus- - - - - -单速率分配滤波器的分数延迟刺激

恒定数值(默认)|数值矢量|'randsweep'|“RampSweep”

单速率分组过滤器的分数延迟刺激,指定为以下之一:

恒定数值 - 测试台,通过从滤波器对象获得的常数值驱动分数延迟输入信号。

数值矢量 - 测试台驱动来自此矢量的分数延迟输入信号。您可以将向量指定为返回向量的函数调用。向量必须与测试台信号相同。

'randsweep'-试验台通过使用在0到1的范围内递增的值向量来驱动分数延迟输入信号。这个刺激信号与滤波器的输入信号有相同的持续时间,但变化速度较慢。从矢量获得的每个分数延迟值保持输入信号总持续时间的10%。“RampSweep”-试验台通过使用从0到1的随机值向量来驱动分数延迟输入信号。这个刺激信号与滤波器的输入信号有相同的持续时间,但它的变化速率较慢。从矢量获得的每个分数延迟值保持输入信号总持续时间的10%。

依赖性

此属性仅适用于GenerateHDLTestBench属性设置为“上”.

TestBenchRateStimulus- - - - - -对CIC滤波器的输入刺激率

最大速率变化因子(默认)|整数

级联梳状积分器(CIC)滤波器的速率输入刺激,指定为最大速率变化因子或整数。如果不指定TestBenchRateStimulus,编码器假定过滤器设计为预期的最大速率。抽取因子(用于CIC Deadimator)或插值因子(用于CIC插值器)被设置为此最大速率变化因子。

看到可变速率CIC滤波器.

依赖性

此属性仅适用于可变速率CIC滤波器,当时GenerateHDLTestBench和addrateport.属性设置为“上”.

削皮

generatecosimblock.- - - - - -生成模型金宝app®HDL Cosimulation块的模型

'离开'(默认)|“上”

生成HDL协同仿真金宝app模块的Simulink模型,指定为'离开'或“上”.生成的Simulink模型包金宝app含两个HDL Cosimulation块:一个用于导师图形®MODELEIM®一个用于疾病的终止®.编码器配置这些块以符合所选筛选器的端口和数据类型接口。使用这些模块在Simulink中使用所需的HDL模拟器来模拟您的设计。金宝app

依赖性

此功能需要HDL Verifier™许可证。

GenerateCosimmodel.- - - - - -生成实现过滤器和H金宝appDL Cosimulation块的Simulink模型

“没有”(默认)|'modelsim'|'尖锐'

生成已实现滤波器的金宝appSimulink模型和HDL协同仿真模块,具体为“没有”,'modelsim', 或者'尖锐'.当您将此属性设置为时'modelsim'或'尖锐',编码器生成并打开Simulink模型。金宝app该模型包含所选模拟器的HDL协同仿真块,以及滤波器设计的行为实现。该模型应用生成的输入刺激,并将EDA模拟器的输出与行为滤波器子系统的输出进行比较。您可以使用与生成的HDL测试台相同的属性来定制输入刺激和误差范围。

看到用HDL模拟器生成协同仿真金宝app的Simulink模型.

依赖性

此功能需要HDL验证许可证。

尖端

如果你用这个函数fdhdltool.生成HDL代码时,可以在试验台在“生成HDL”对话框中的选项卡。

matlab命令

您点击了一个对应于这个MATLAB命令的链接:

在MATLAB命令窗口中输入它来运行命令。Web浏览器不支持MATLAB命令。金宝app

你也可以从以下列表中选择一个网站:

如何获得最佳网站性能

请选择表现最佳的中国网站(中文或英文)。MathWorks的其他国家网站并没有针对您所在位置的访问进行优化。