从系统测试在SystemVerilog中生成功能覆盖验证调用

这个例子演示了如何使用模型仿真来测试投影仪控制系统,以及如何生成一个SystemVerilog DPI组件来满足控制器的一些高级要求,这些要求在test Sequence块中指定。这将允许在HDL模拟器中以最小的努力重用用于模型模拟的需求验证。

模型取自实例投影仪控制器测试使用验证和实时测试(金宝app仿真软件测试)附带Simulink Te金宝appst™,并简化为仅显示需求场景4。

要了解有关验证语句的更多信息,请参见使用验证语句评估模型仿真(金宝app仿真软件测试).

其他先决条件

除了规定的产品要求外,本示例还要求:

一个金宝app支持的HDL模拟器。看到UVM和DPI组件生成需求.

一个金宝app受支持的C编译器。看到选择和配置C或c++编译器(金宝app仿真软件编码器).

概述

测试使用执行顶级控制器模型的测试序列根据其需求验证控制器。控制器采用按键输入和温度传感器输入,输出控制风扇、风扇转速和投影灯的信号。

目标是生成SystemVerilog DPI组件来捕获控制器的高级别需求编号4。有关需求的更多信息,请参阅word文档sltestProjectorCtrlReqs.docx在上面提到的例子中。

要求4在投影仪温度(Tproj)高时尝试打开和关闭投影仪。该场景在Test Sequence块中有以下步骤:

设置投影仪温度为50摄氏度。

试着打开。

系统不应该打开。

把温度设为摄氏50度。

试着关掉。

系统应该关闭。

下面的图片显示了上述需求的测试平台以及如何实现验证用于检查投影仪是否根据场景打开或关闭。

建立代码生成模型

模型和测试台预先配置了一个SystemVerilog DPI系统目标文件(systemverilog_dpi_grt.tlc)。打开测试线束Req_scenario_4通过执行:

测试文件=“svdpi_sltestProjectorCtrlTests.mldatx”;testHarness =“Req_scenario_4”;模型=“svdpi_sltestProjectorController”;open_system(模型)

testHarness sltest.harness.open(模型)

生成SystemVerilog DPI组件

在Req_scenario_4测试工作台,右键单击Req_4子系统块,其中包含测试序列块和选择。C/ c++ Code ->构建这个子系统.

点击构建在出现的对话框中。

生成的C代码Req_4子系统,以及一个名为“Req_4_build/Req_4_dpi. zip”的SystemVerilog DPI包装器和包文件。sv”和“Req_4_build / Req_4_dpi_pkg.sv”。

注意,一些验证警告将被触发,这将在后面解释。

或者,你可以通过执行以下命令来生成组件:

slbuild (“Req_scenario_4 / Req_4”);

在HDL模拟器中运行生成的测试台

对于本例,将使用ModelsSim/QuestaSim模拟器。有关如何运行测试台的详细说明,请参阅开始SystemVerilog DPI组件生成.

cdReq_4_build / dpi_tb!Vsim -c -do run_tb_mq。#在控制台模式下运行ModelSim/QuestaSimcd. . / . .

检查HDL模拟输出并注意以下内容:

一条信息消息显示将为组件中的2个验证调用收集功能覆盖率

当温度超过限制时,控制器无法关闭,标记了一个错误。

由于SystemVerilog仿真结果与Simulink仿真结果相匹配,所以测试被标记为PASSED。金宝app

功能覆盖表明第一次验证调用实现了覆盖,但第二次验证调用没有实现。

总体功能覆盖目标没有得到满足。

误差与Simulink中的仿真结果一致(见下)。金宝app打开测试管理器显示,当温度超过限制时,按下on_off按钮时控制器无法关闭。要打开测试管理器,您可以执行:

sltest.testmanager.load(测试文件);sltest.testmanager.view;

解决故障需要修改主模型中的OnOff检查子系统。其他要求,verify_sc4_on,如Simulink Test和SystemVerilog覆盖结果所示。金宝app

跟踪SystemVerilog错误返回到Simulink金宝app

如果你想跟踪生成错误的验证语句到Simulink,你需要从错误消息中找到Simulink标识符(SID),如下所示:金宝app

一旦在测试序列块中找到步骤id的SID,就可以使用Simulink编程api突出显示相应的块。金宝app有关更多信息,请参见金宝app动态仿真模块标识符(金宝app模型).执行如下命令:

金宝appSimulink.ID.hilite (“Req_scenario_4:32:60”);

这将突出显示如下所示的相关块。

过滤特定的验证评估

要在HDL模拟器中筛选任何验证评估状态检查,请将想要筛选的评估的SID作为一个plusargs参数提供给HDL模拟器。这样的筛选将意味着没有错误,也不会检查评估的覆盖范围。例如,你可以过滤错误verify_sc4_off通过向HDL模拟器提供参数“+Req_scenario_4:32:60”来给出。您可以通过环境变量来实现这一点,这样就不必修改生成的脚本。

%清除影响SV模拟的环境变量setenvEXTRA_SVDPI_COMP_ARGSsetenvEXTRA_SVDPI_SIM_ARGS

%过滤失败的验证()setenvEXTRA_SVDPI_SIM_ARGS+ Req_scenario_4:32:60 = 1cdReq_4_build / dpi_tb!Vsim -c -do run_tb_mq。#在控制台模式下运行ModelSim/QuestaSimcd. . / . .

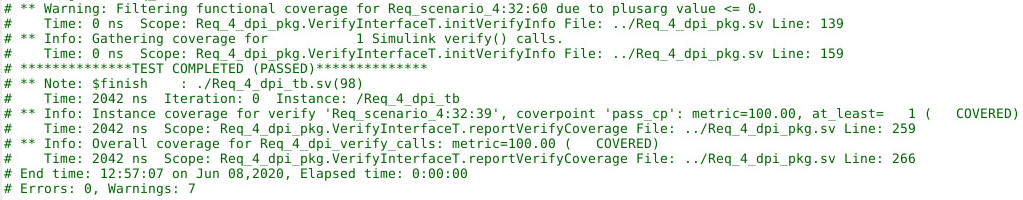

注意,HDL模拟现在显示:

一个警告,其中一个验证评估正在被过滤

将为其他评估收集覆盖率的信息消息

不再有任何错误。

由于SystemVerilog仿真结果与Simulink仿真结果相匹配,所以测试被标记为PASSED。金宝app

功能覆盖率显示已为启用的评估实现了覆盖率

总体功能覆盖目标得到满足。

增加特定验证评估的覆盖率目标

您还可以通过向+ arg提供一个正值来更改任何评估所需的功能覆盖目标。默认目标是查看验证调用的至少1个PASS状态。如果你想确保至少有2个验证PASS状态检查,你可以提供一个“2”作为加参数值。

%清除影响SV模拟的环境变量setenvEXTRA_SVDPI_COMP_ARGSsetenvEXTRA_SVDPI_SIM_ARGS

%过滤失败的|,验证|,并为其他|验证|设置覆盖目标为2setenvEXTRA_SVDPI_SIM_ARGS“+ Req_scenario_4:32:60 = 1 + Req_scenario_4:32:39 = 2”cdReq_4_build / dpi_tb!Vsim -c -do run_tb_mq。#在控制台模式下运行ModelSim/QuestaSimcd. . / . .

注意,HDL模拟现在显示了未过滤的验证没有达到至少2次通过的覆盖率目标,因此整个测试也没有达到。

记录所有验证评估的通过、失败和未测试状态

您可以为所有未过滤的状态检查添加日志输出验证通过添加+VERBOSE_VERIFY + arg调用。如果需要检查UNTESTED、PASS和FAIL验证状态值的时间和分布,这可能很有用。

%清除影响SV模拟的环境变量setenvEXTRA_SVDPI_COMP_ARGSsetenvEXTRA_SVDPI_SIM_ARGS

%记录每一个状态检查。setenvEXTRA_SVDPI_SIM_ARGS+ VERBOSE_VERIFYcdReq_4_build / dpi_tb!Vsim -c -do run_tb_mq。#在控制台模式下运行ModelSim/QuestaSimcd. . / . .

注意,HDL模拟现在将每个UNTESTED和PASS状态检查值显示为SystemVerilog信息消息和每个FAIL状态都是一个SystemVerilog错误。

结论

SystemVerilog DPI组件生成和来自Simulink Test™的测试序列块可用于将验证逻辑从Simulink迁移到HDL模拟器,且金宝app工作量很小。