基于HDL工作流顾问的FIL仿真金宝app

步骤1:启动HDL Workflow Advisor

按照说明调用HDL工作流顾问。看见HDL Workflow Advisor入门(HDL编码器).

注意

你必须有一个HDL编码器™ 使用HDL Workflow Advisor生成HDL代码的许可证。

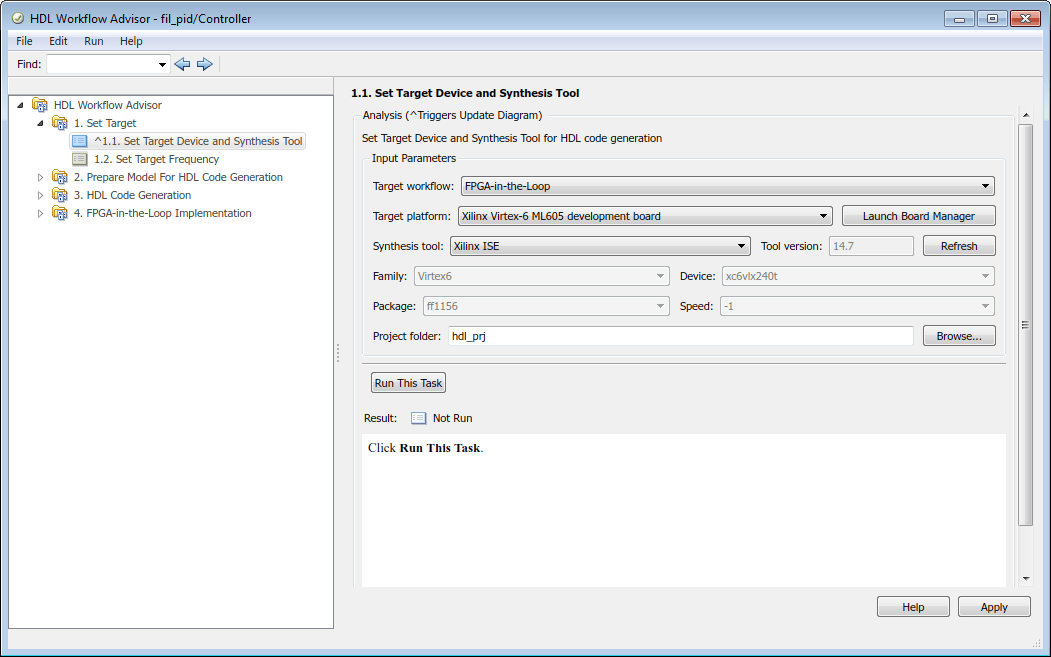

第二步:设定目标和目标频率

在步骤1中,设定目标点击1.1设定目标装置及合成流程并执行以下操作:

选择

FPGA在环从目标工作流.在下面目标平台,从下拉列表中选择一个开发板。家庭,装置,包裹,和速度由HDL工作流顾问填写。如果您尚未下载HDL验证程序™ FPGA板支持包,选择金宝app

多拿些木板. 下载完FPGA板支持包后返回此步骤。金宝app对于文件夹,输入要将项目文件保存到的文件夹名称。默认值为

高密度脂蛋白在当前工作文件夹下。

在步骤1.1中选择FIL目标后,单击1.2设定目标频率.

设置目标频率(MHz)在FPGA上实现的设计的时钟速度。可用频率范围如所示频率范围(MHz)参数英特尔公司®董事会和Xilinx®板,工作流顾问检查请求的频率与请求板的可能频率。如果请求的频率不适用于此电路板,Workflow Advisor将返回一个错误并建议一个备用频率。为Xilinx Vivado®-金宝app支持的主板或PCI Express®板,工作流顾问无法检查频率。合成工具会尽最大努力尝试所需的频率,但如果无法达到指定的频率,则可以选择备用频率。默认值为

25兆赫。

第3步:为生成HDL代码准备模型

在步骤2,为HDL代码生成准备模型,执行步骤2.1–2.4,如中所述为HDL代码生成准备模型概述(HDL编码器).

此外,执行步骤2.5检查FPGA在环兼容性验证模型是否与FIL兼容。

步骤4:生成HDL代码

在第3步,HDL代码生成,执行步骤3.1和3.2,如中所述HDL代码生成概述(HDL编码器).

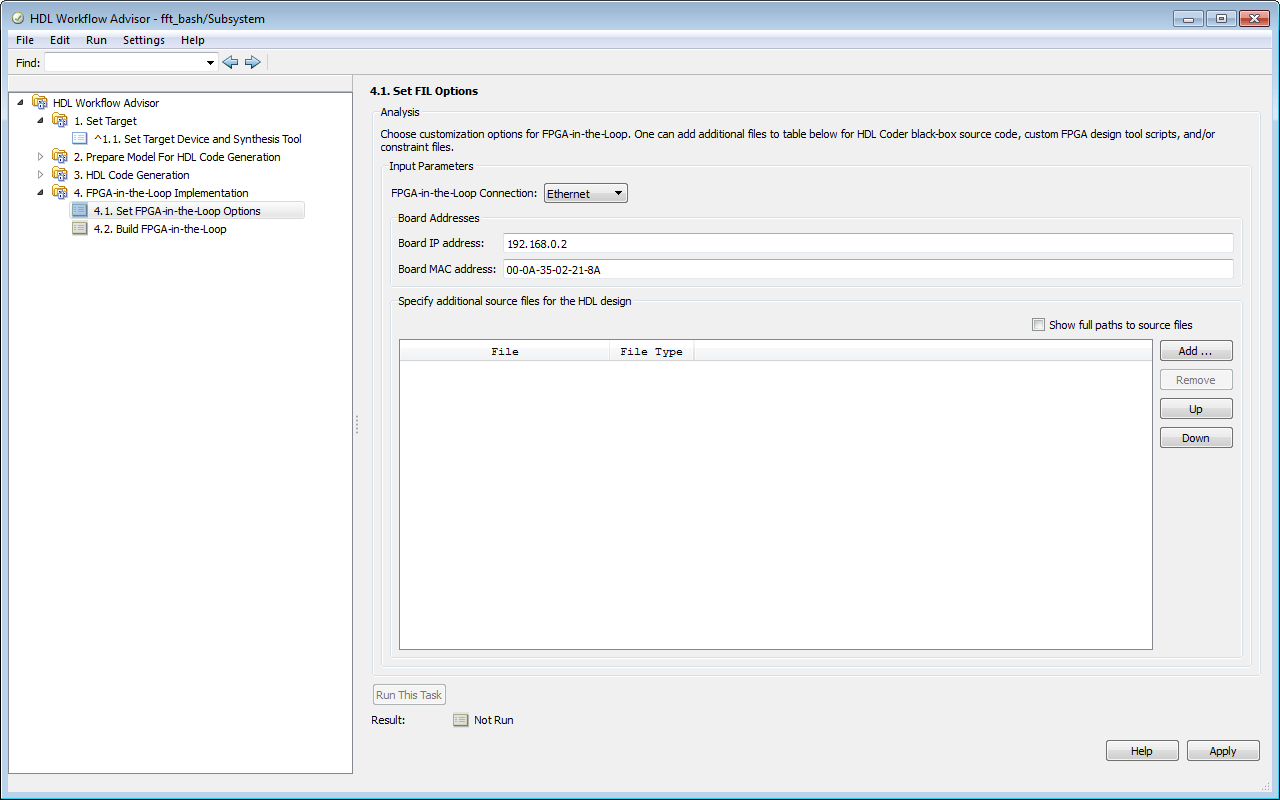

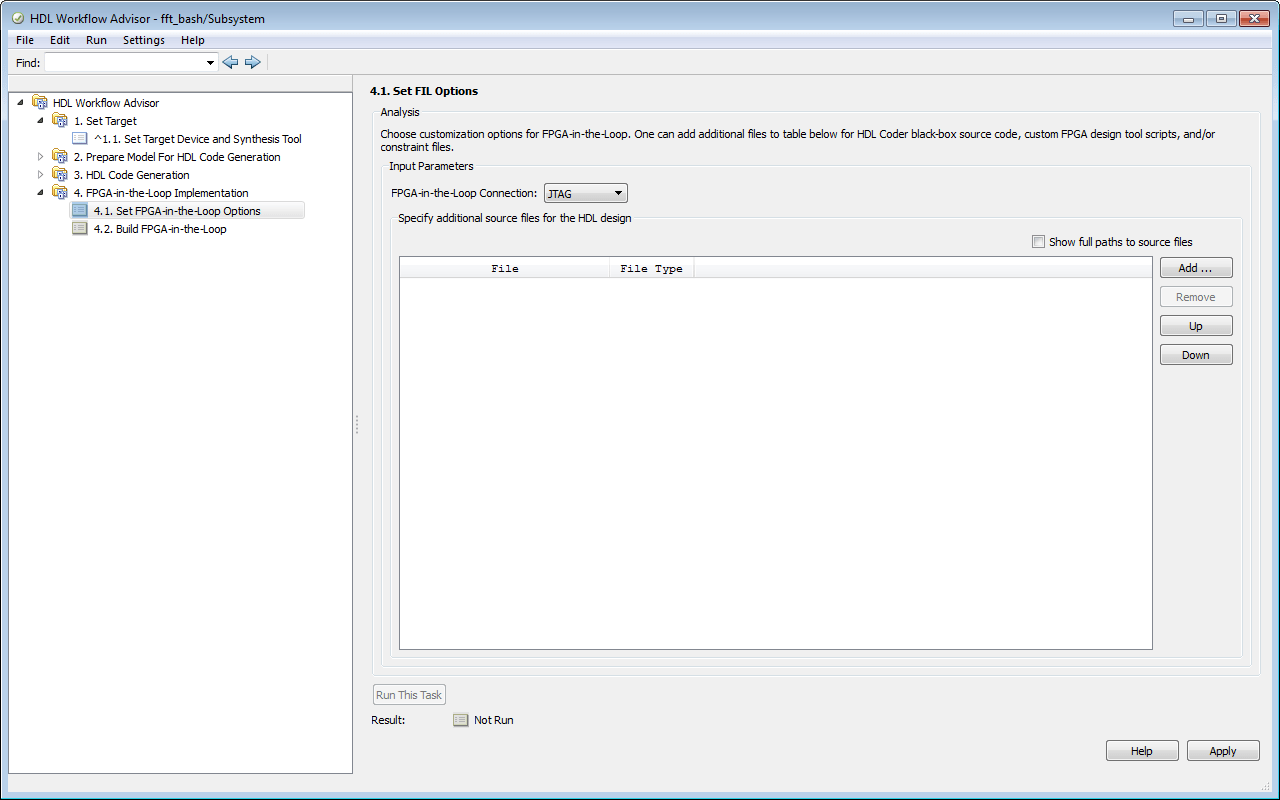

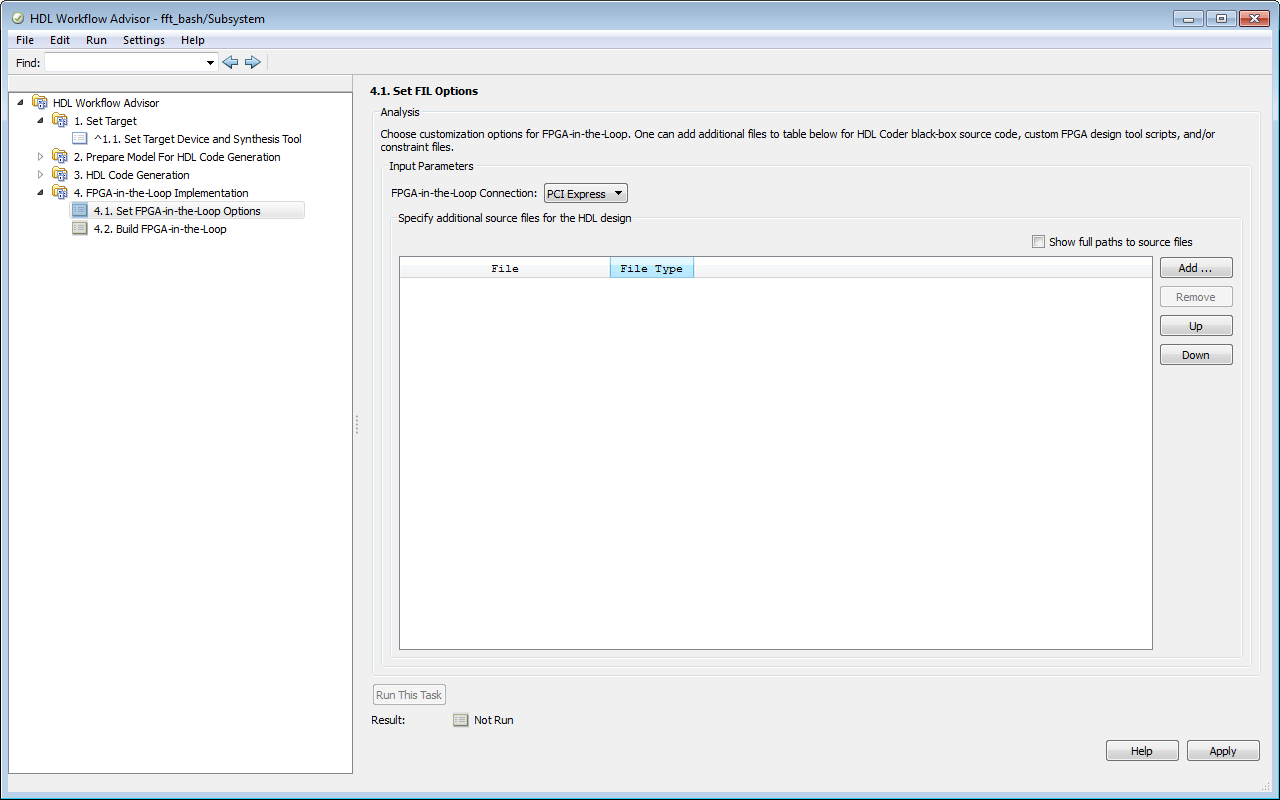

第5步:设置FPGA在环选项

在步骤4.1中,设置FPGA在环选项,如有必要,请更改这些选项:

FPGA在环连接:FIL模拟连接方法。下拉菜单中的选项会根据所选目标板支持的连接方法进行更新。如果目标板和HDL验证器支持连接,您可以选择金宝app

以太网,JTAG公司或PCI Express.董事会地址:

选择以太网连接时,如有必要,可以调整主板IP和MAC地址。

选项 说明书 板IP地址 如果不是默认IP地址(192.168.0.2),则使用此选项设置板的IP地址。

如果默认板IP地址(192.168.0.2)正被另一个设备使用,或者您需要不同的子网,请根据以下准则更改板IP地址:

子网地址(通常是板IP地址的前三个字节)必须与主机IP地址的子网相同。

板IP地址的最后一个字节必须与主机IP地址的最后一个字节不同。

板IP地址不得与其他计算机的IP地址冲突。

例如,如果主机IP地址为192.168.8.2,则可以使用192.168.8.3(如果可用)。

板MAC地址 在大多数情况下,您不需要更改板MAC地址。如果将多个FPGA开发板连接到单个主机,请更改任何其他板的板MAC地址,使每个地址都是唯一的。每个板必须有一个单独的NIC。

要更改主板MAC地址,请单击板MAC地址领域指定一个不同于连接到计算机的任何其他设备的地址。要获取特定FPGA开发板的板MAC地址,请参阅板上的标签或查阅产品文档。

为HDL设计指定其他源文件:

指示DUT使用的其他源文件添加. 要(可选)显示源文件的完整路径,请选中标题为显示源文件的完整路径. HDL Workflow Advisor尝试标识源文件类型。如果文件类型不正确,可以通过从文件类型下拉列表。

以太网FIL

JTAG上的FIL

结束PCI Express

第六步:生成FPGA编程文件和FPGA在环模型

在步骤4.2中,在环中构建FPGA点击运行此任务.

在生成过程中,会发生以下操作:

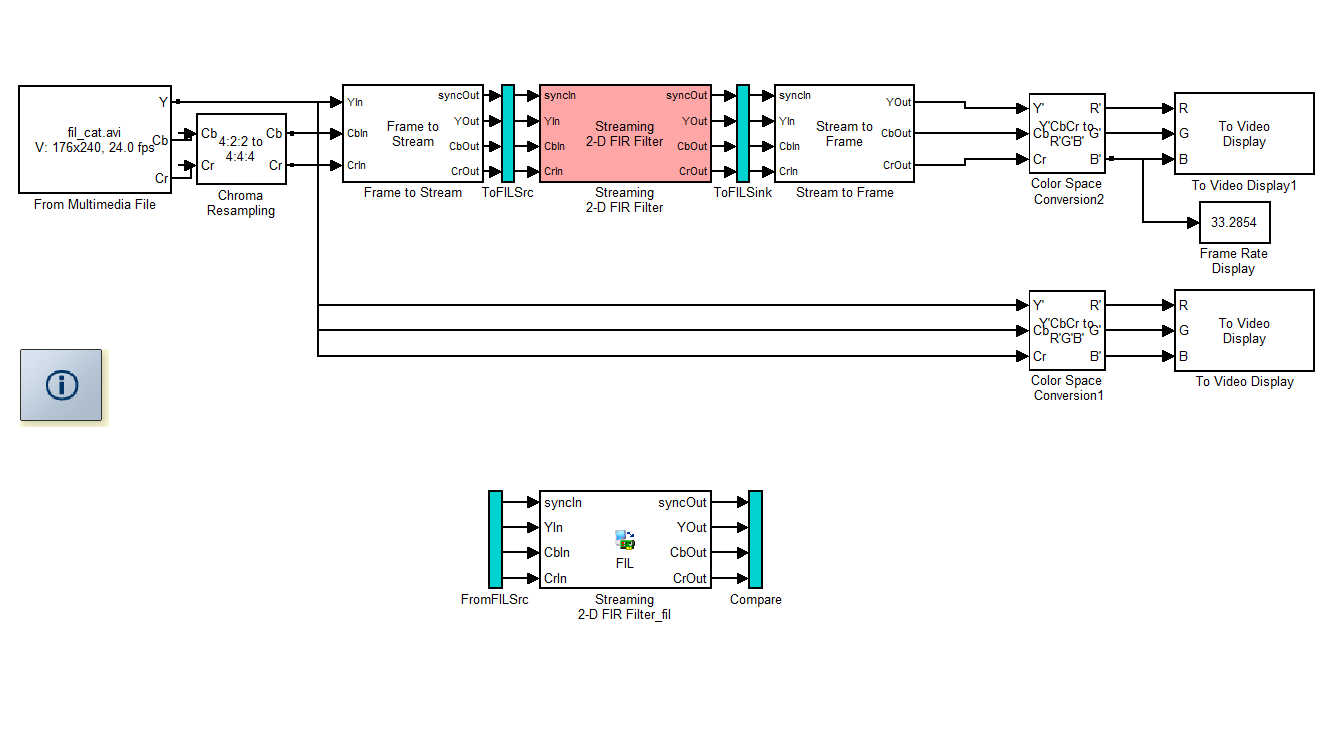

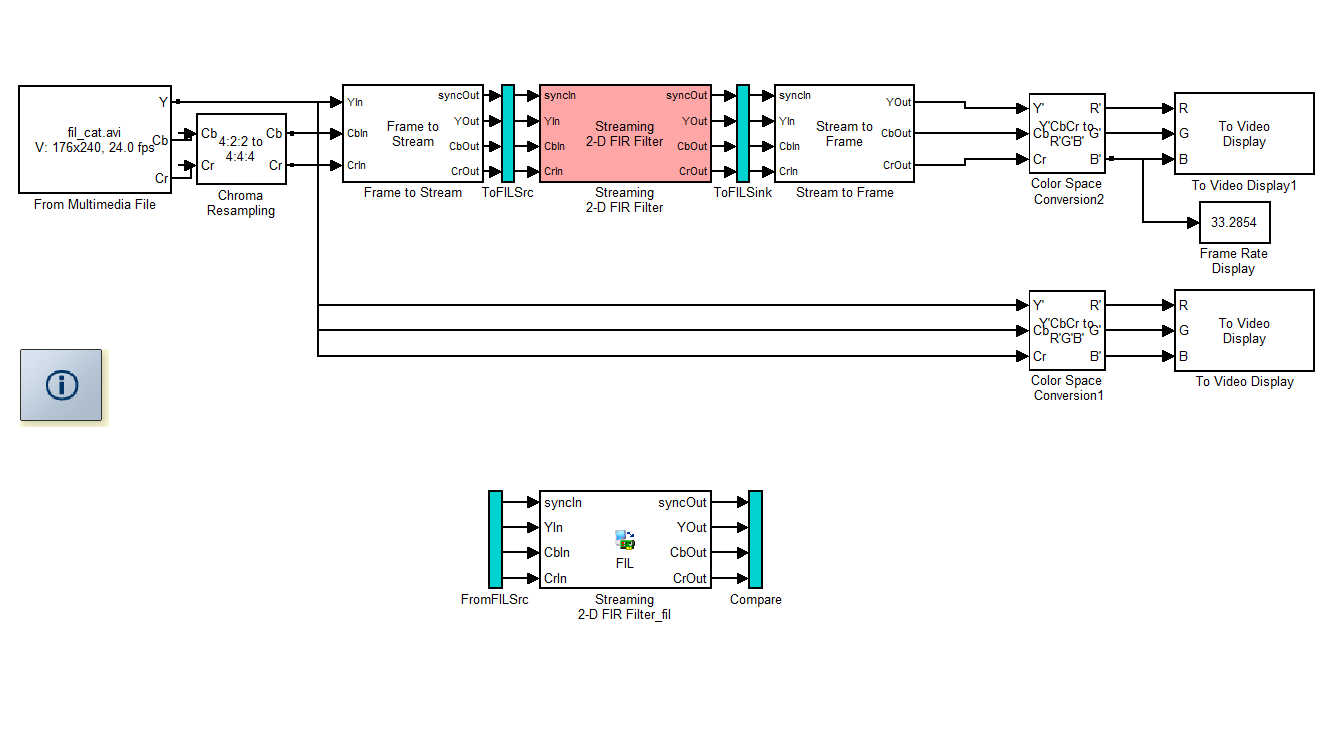

HDL工作流顾问生成一个以顶级模块命名的FIL块,并将其放置在新模型中。下一个图显示了包含FIL块的新模型的示例。

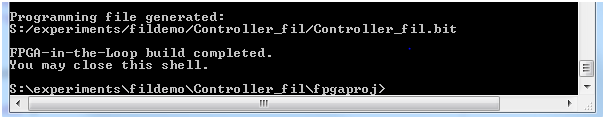

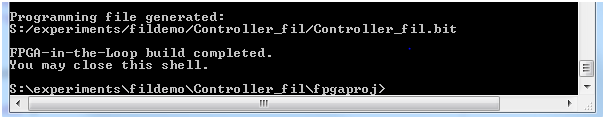

生成新模型后,HDL Workflow Advisor将打开一个命令窗口:

在这个窗口中,FPGA设计软件执行合成、拟合、PAR和FPGA编程文件生成。

进程完成后,命令窗口中会显示一条消息,提示您关闭窗口。

HDL工作流顾问围绕生成的FIL块构建一个测试台模型。

第七步:将编程文件加载到FPGA上

确保您的FPGA开发板已按照板制造商文档的指示安装、通电并连接到您的机器。然后,执行以下步骤对FPGA进行编程:

双击Simulink中的FIL块金宝app®打开遮罩模型。

上主要选项卡,单击负载将编程文件下载到FPGA。

加载过程可能需要几分钟,这取决于子系统的大小。对于非常大的子系统,这个过程可能需要一个小时或更长的时间。

有关更多故障排除提示,请参阅将编程文件加载到FPGA上.

步骤8:运行模拟

在Si金宝appmulink中,在模拟选项卡,单击跑. FIL模拟的结果应与Simulink参考模型或原始HDL代码的结果相匹配。金宝app

注意

关于初始化:Simulink每次从时间0开始,这意味金宝app着Simulink中的RAM被初始化为0。然而,这在硬件上是不正确的。如果您的设计中有RAM,则第一次模拟将与Simulink匹配,但任何后续运行都可能不匹配。

解决方法是在重新运行模拟之前重新加载FPGA位流。要执行此操作,请单击负载在FIL-block-mask上。