从FPGA执行的内存性能信息

与模拟中生成的内存性能图类似,您可以从FPGA上运行的设计中收集内存互连流量信息。然后可以生成类似的性能图。控件中还可以捕获要查看的内存事务信息逻辑分析仪工具类似突发事务从内存控制器模拟。使用这些图来监控真实的内存性能,调试和改进设计,并与仿真中获得的内存性能进行比较。

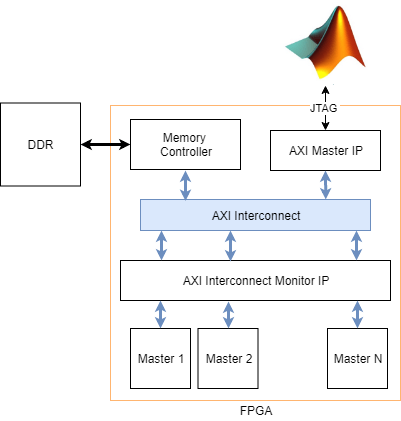

包括一个AXI互连监控(AIM) IP在您的设计中,在模型的配置参数中,选择包括AXI互连监视器选择下硬件实现>目标硬件资源>FPGA设计(调试).的AXI互连监控IP在FPGA上运行时从设计中收集信息。您可以从MATLAB查询此信息®通过使用JTAG连接。您的FPGA中的所有内存主机都连接到AXI互连监控IP。这些大师可以包括内存通道和内存流量发生器块,您为其生成的HDL代码或设计中的任何其他主程序。

的SoC建设者工具为您的设计生成一个JTAG测试台脚本。脚本从AXI互连监控并启动性能图应用程序,该应用程序绘制带宽、突发数和事务延迟的内存性能图。这些图与仿真中的内存性能图相似。您还可以修改脚本来收集和显示内存事务波形,类似于模拟中内存控制器的突发波形。有关模拟内存性能的信息,请参见仿真性能的情节和缓冲和突发波形.

例如,请参见使用流量生成器分析内存带宽,展示了如何在仿真和在FPGA上运行时监控内存性能。生成的脚本SoC建设者工具使用JTAG连接来启用设计中的任何流量生成器,然后从AXI互连监控尽可能快地获取IP。采样间隔取决于JTAG延迟,通常是10毫秒到20毫秒。脚本然后显示类似于内存控制器在你的模拟中。该图显示了每个主机的带宽、突发次数和事务延迟。

请注意

AXI主机本身没有连接到AXI互连监控.因此,硬件诊断不包括仅测试台主机的内存使用图,仅测试台主机使用预先确定的数据初始化内存。

内存性能的情节

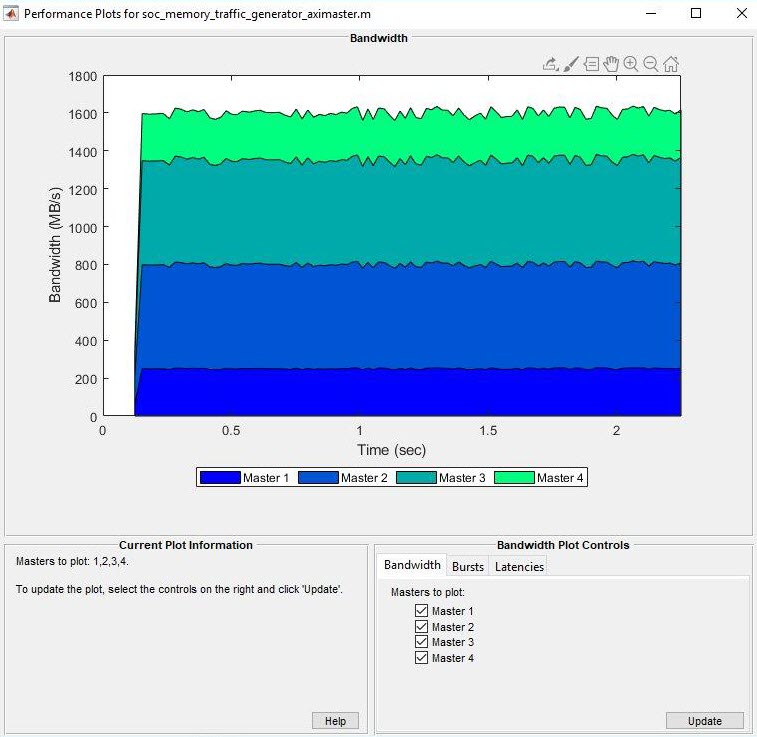

脚本从AXI互连监控并启动性能图应用程序。

内存带宽的情节

在带宽选项卡,选择要为其绘制带宽图的主机。点击创建图查看所选主机在运行时期间的带宽,单位为每秒兆字节。这个图显示了使用流量生成器分析内存带宽的例子。

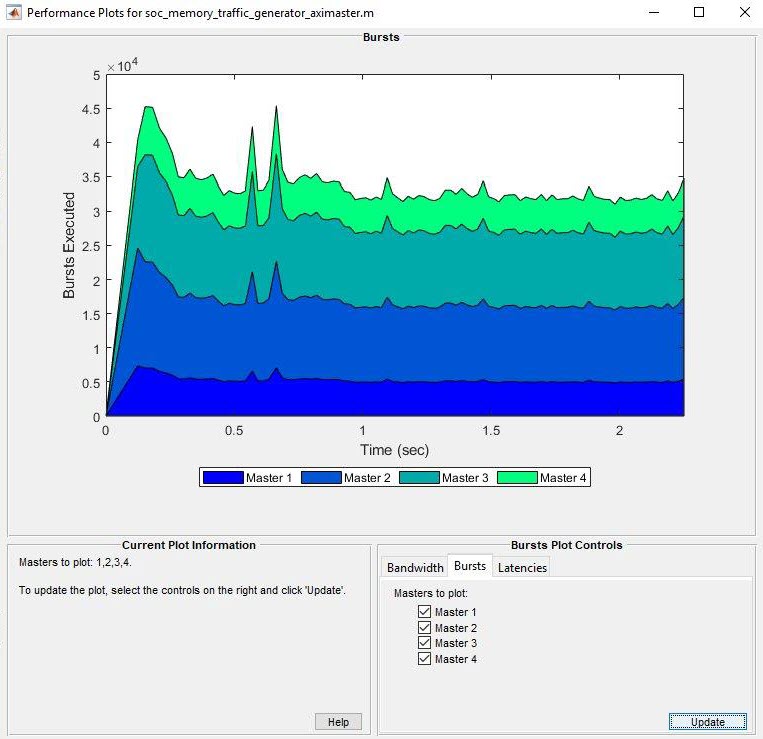

内存爆炸阴谋

在爆发选项卡,选择要为其绘制爆发图的主控文件。点击创建图查看在运行时期间为选定的主服务器执行的突发数。这个图显示了突发计数使用流量生成器分析内存带宽的例子。

内存延迟的情节

在延迟选项卡,选择要为其绘制延迟图的主服务器。点击创建图查看所选主机在运行时期间的延迟。这个图像显示了总的延迟硕士1在使用流量生成器分析内存带宽的例子。然后可以放大以分析峰值瞬时延迟。

你可以从以下选项中选择:

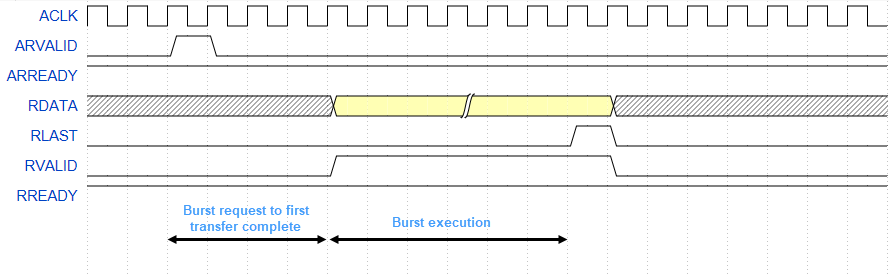

突发请求第一次传输完成-这个选项显示从主服务器发出事务请求到第一次数据传输所花费的时间。此延迟说明仲裁或互连延迟。

破裂的执行-该选项显示从第一次传输数据到突发最后一次传输的时间。

完成最后一次传送-该选项显示从上次传输到完成交易所花费的时间。对于读事务,它是0。

瞬时总延迟-该选项显示每个突发的离散的总延迟测量。

绘制的每个延迟值是各自延迟的平均值,从一个采样间隔内的内存事务中测量。下图显示了硬件上的一个AXI4主协议写和读事务,显示了每一个延迟。

写事务

读事务

读事务,突发最后一次传输以完成延迟是零。

数据溢出

在配置文件模式下,collectMemoryStatistics函数对内存度量进行采样:每次采样后从硬件中获取的带宽、突发和延迟值。在此之后,该函数将重置度量计数器,然后为下一个示例再次启动计数器。如果任何度量计数器超过2的限制32- 1在采样间隔内,计数器溢出,对应的采样用表示*的阴谋。

破裂的波形

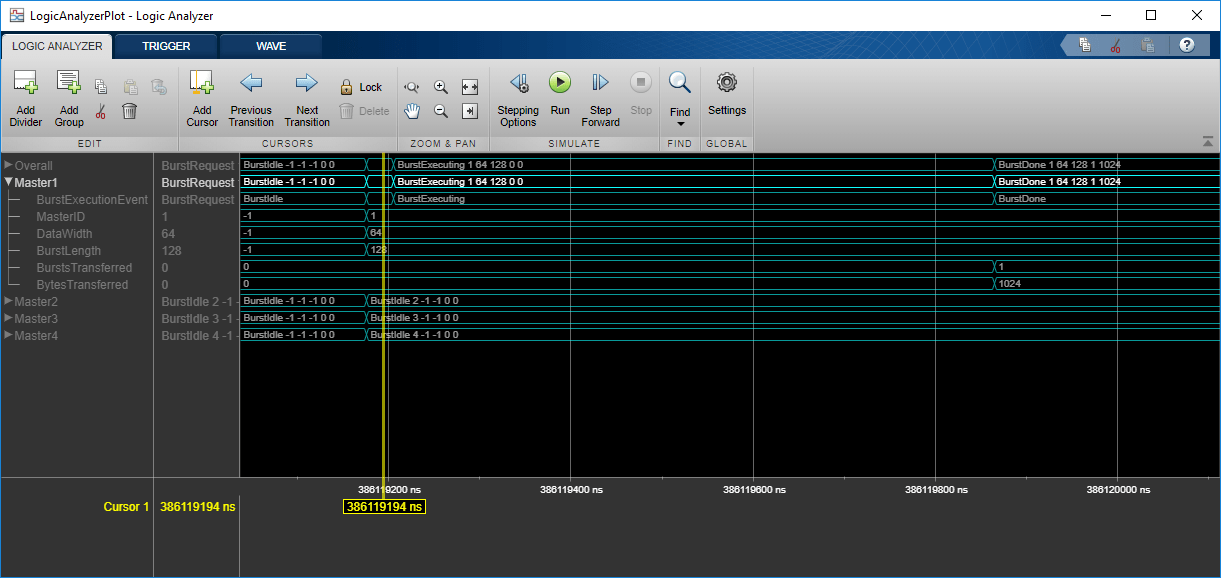

您还可以修改生成的脚本来配置AXI互连监控为每个突发事务收集事件数据。您可以查看这些事件逻辑分析仪波形查看器检查仲裁行为。指定要捕获的事务的数量,跟踪捕捉深度,在模型的配置参数中,下硬件实现>目标硬件资源>FPGA设计(调试).

波形显示事件类型(BurstIdle,BurstRequest,BurstExecuting,或BurstDone)和突发事务的以下参数:

MasterID——发出请求的内存主服务器的ID号DataWidth——以位为单位的数据宽度BurstLength——突发请求中的数据字数BurstsTransferred——此请求中的突发数(仅与BurstDone事件)BytesTransferred——这个请求的字节数(仅与BurstDone事件)

你可以将这些波形与从你的内存控制器在模拟块。

配置和查询axis Interconnect Monitor

的AXI互连监控(AIM)是一个IP核,它为基于axis的FPGA设计收集性能指标。创建一个socIPCore对象来设置和配置AIM IP,并使用socMemoryProfiler对象检索和显示数据。

有关如何使用MATLAB作为axis Master在设计中配置和查询AIM IP的示例,请参见使用流量生成器分析内存带宽.具体地说,回顾soc_memory_traffic_generator_axi_master.m用于配置和监控设备上的设计的脚本。

选择内存监控模式

的AXI互连监控可以收集两种类型的数据。选择配置文件模式来收集平均事务延迟、字节计数和突发。在此模式下,您可以打开性能绘图工具,将性能绘图工具配置为对带宽、突发数和事务延迟进行绘图。选择跟踪模式来收集详细的内存事务事件数据,并将数据作为波形查看。

perfMonMode =“配置文件”;%或“跟踪”

配置AXI Interconnect Monitor

要从生成的FPGA设计中获得诊断性能指标,必须从MATLAB设置到设备的JTAG连接。加载一个.mat包含从单板配置参数派生的结构的文件。该文件由SoC建设者工具。这些结构描述内存互连和主配置,如缓冲区大小和地址。使用socHardwareBoard对象来设置JTAG连接。

负载(“soc_memory_traffic_generator_zc706_aximaster.mat”);hwObj = socHardwareBoard (“Xilinx Zynq ZC706评估试剂盒”,“连接”、假);AXIMasterObj = socAXIMaster (hwObj);

socIPCore对象提供执行此初始化的函数。接下来,设置一个socMemoryProfiler对象来收集指标。apmCoreObj = socIPCore (AXIMasterObj perf_mon,“PerformanceMonitor”,“模式”, perfMonMode);初始化(apmCoreObj);profilerObj = socMemoryProfiler (hwObj apmCoreObj);

检索诊断数据

要从FPGA上运行的设计中检索性能指标或信号数据,请使用socMemoryProfiler对象的功能。

为配置文件模式,调用collectMemoryStatistics函数循环。

NumRuns = 100;为n = 1:NumRuns collectMemoryStatistics(profilerObj);结束

为跟踪模式,调用collectMemoryStatistics函数一次。该函数阻止IP将事务写入FIFOAXI互连监控尽管事务继续在互连上进行。设置事务FIFO的大小,跟踪捕捉深度,在模型的配置参数中,下硬件实现>目标硬件资源>FPGA设计(调试).

collectMemoryStatistics (profilerObj);

可视化性能指标

属性可视化性能数据plotMemoryStatistics函数。在配置文件模式下,此功能将打开一个性能绘图工具,您可以配置该工具来绘图带宽、突发计数和平均事务延迟。在跟踪模式下,此函数打开逻辑分析仪查看突发事务事件数据的工具。

plotMemoryStatistics (profilerObj);

另请参阅

内存控制器|socMemoryProfiler|collectMemoryStatistics|plotMemoryStatistics