出口自定义参考设计

此示例显示如何通过使用SOC BlockSet™从SoC模型导出自定义参考设计rocexportreferencedesign.功能。创建自定义参考设计后,使用HDL工作流程顾问从HDL编码器™的工具将IP内核集成到参考设计中。

设计任务

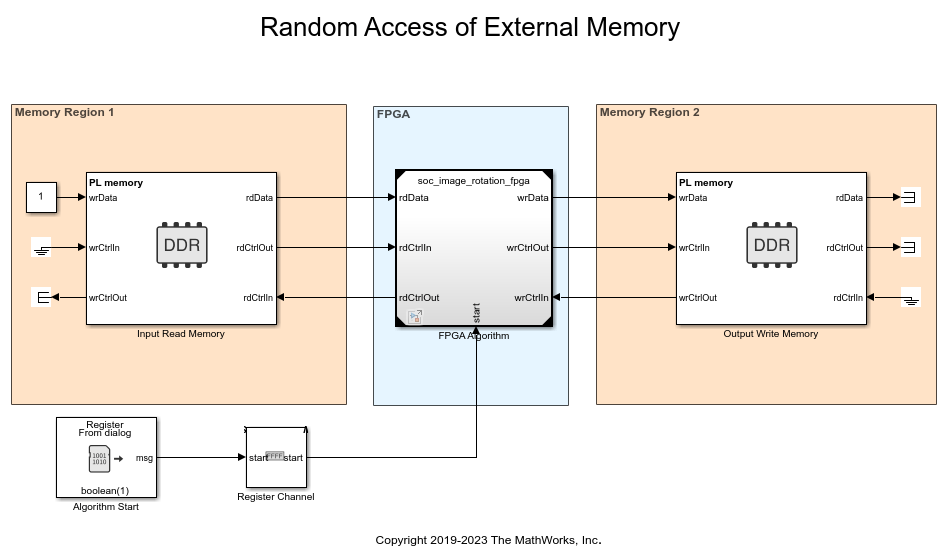

此示例使用模型soc_image_rootation.生成自定义参考设计。该模型具有外部内存和FPGA DUT。DUT包含AXI4主读取界面和AXI4主写入界面,以对内存执行读写操作。有关模型的完整描述,请参阅随机访问外部存储器。该模型也使用一个Socaximaster.要从主计算机读取和写入外部存储器。

从此模型导出自定义参考设计时,DUT不包含在参考设计中,并曝光DUT的接口。生成参考设计后,您可以使用自定义IP集成HDL工作流程顾问工具。您的自定义IP必须具有与FPGA算法块相同的接口。

打开模型以查看顶级模型的结构和FPGA算法块的接口。

Open_System('soc_image_rotation');

为自定义参考设计导出准备SOC模型

在Si金宝appmulink®中,单击打开“配置参数”对话框模型设置在这一点造型标签。然后,请按照以下步骤准备自定义参考设计导出的SOC模型。

在左窗格中,选择硬件实现。

放硬件板匹配您的电路板(如果您没有使用

Xilinx Zynq ZC706评估套件)。在下面功能为所选的硬件板设置, 选择SoC块集。

扩张目标硬件资源, 选择FPGA设计(顶级),然后选择包括基于主机的交互的“Matlab Axi Master”IP。

因为此SOC模型不包括处理器,因为清除包括处理系统。如果您的SOC模型包括处理器子系统,则选择此选项。

在里面IP核心时钟频率(MHz)框,在MHz中指定IP核心时钟频率。

选择FPGA设计(MEM通道)和集合互连数据宽度(位)到

32.。

出口自定义参考设计

导出模型的自定义参考设计soc_image_rootation.通过使用rocexportreferencedesign.功能。在MATLAB命令提示符下输入此代码:

rocexportreferencedesign('soc_image_rotation')

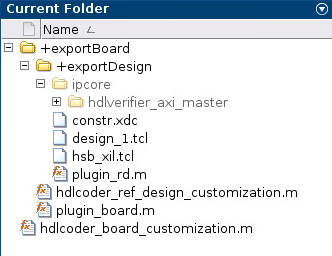

该函数在当前文件夹中生成这些伪像。

董事会注册文件

参考设计注册文件

IP存储库

设计文件

约束文件

将生成的设计文件夹添加到路径

要将生成的设计文件夹添加到MATLAB路径,请右键单击命名的文件夹超模-refdesign., 在哪里超模是顶级SOC模型的名称。然后选择添加到path>选定的文件夹和子文件夹。

将IP内核集成到自定义参考设计中

生成参考设计后,您可以将其保存或将其传递给IP开发人员,以便在电路板上集成和部署其IP。

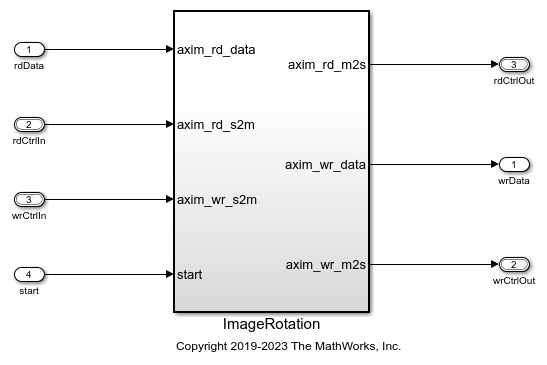

此示例使用图像旋转DUT作为IP。该参考设计适用于具有相同界面的任何IP。

Open_System('soc_image_rotation_fpga');

在Si金宝appmulink中,右键单击ImageOrotation块并选择HDL代码> HDL工作流程顾问打开HDL工作流程顾问工具。

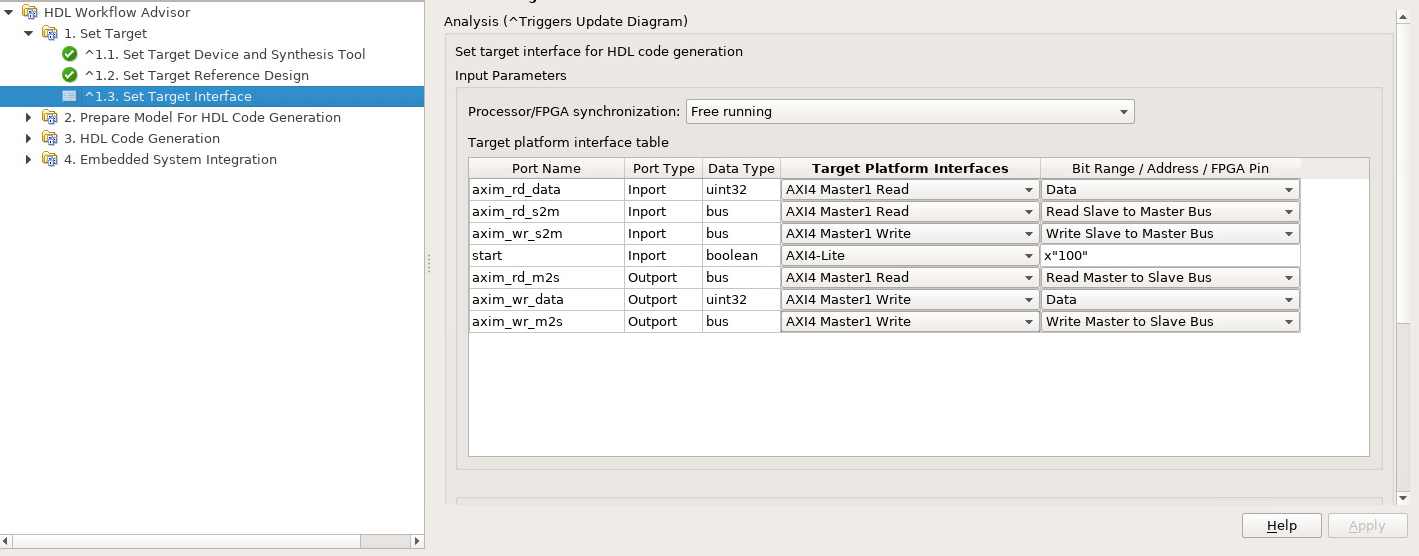

在步骤1.1中,设置目标工作流程到

IP核心生成和目标平台到了由此产生的平台rocexportreferencedesign.功能。对于此示例,请选择Xilinx Zynq ZC706评估套件(由SoC块集生成)。点击运行此任务。

选择步骤1.2。注意参考设计被设置为

从'soc_image_rootation'模型导出的设计。在步骤1.3中,通过将IP中的每个端口连接到参考设计中的相应端口来设置目标接口。

5.继续剩下的剩余步骤HDL工作流程顾问工具。

6.在步骤4.2中生成具有C代码生成的IP核心驱动程序块的软件界面模型, 选择跳过这项任务。对于此示例,选择此值,因为生成的参考设计仅包括FPGA和内存组件。如果参考设计还包括处理系统,请清除此选项。

7.在步骤4.4中,设置编程方法到JTAG.。

8.将主机连接到ZC706板,然后按照工作流程将您的全部设计(IP和自定义参考设计)加载到FPGA。

9.使用MATLAB AXI主站与主机与FPGA交互。

结论

此示例介绍了这些工作流程。

从SOC模型生成参考设计

将IP核心集成到生成的参考设计中HDL工作流程顾问工具

也可以看看

SoC Builder.|rocexportreferencedesign.