从SoC模型导出自定义参考设计

你可以使用socExportReferenceDesign函数从SoC Blockset™模型生成参考设计,避免生成和注册自定义参考设计所需的手动步骤。该函数生成这些工件。

委员会登记文件

参考设计注册文件

IP存储库

设计文件

约束文件

SoC模型可以是这些类型之一。

带有FPGA、内存和可选I/O(无处理器)的SoC模型

带有处理器、FPGA、内存和可选I/O的SoC模型

建立系统的SoC模型

当从SoC模型导出自定义参考设计时,参考设计不包括待测设计(DUT),并暴露到DUT的接口。在生成参考设计之后,您可以使用高密度脂蛋白工作流顾问工具。您的自定义IP必须具有与FPGA算法块相同的接口。

要导出自定义参考设计,首先创建一个SoC模型,以建模系统和可用的I/O板。要创建SoC块集模型,请使用以下方法之一。

使用SoC Blockset模板创建模型(推荐)。有关更多信息,请参见使用模板创建SoC模型.

从头开始构建SoC模型。有关更多信息,请参见创建SoC项目申请.

在模型中包含一个DUT子系统。这个子系统必须具有与您正在开发的IP核相同的接口。因为生成的参考设计不包括DUT子系统,所以DUT可以是一个简单的模型,也可以只是一个直通块。

准备SoC模型用于参考设计导出

您可以在导出的参考设计中使用MATLAB作为axis主特性来与来自主机的SoC设备进行交互。在仿真金宝app软件®,单击打开“配置参数”对话框模型设置在建模选项卡,并在左侧窗格中选择硬件实现.然后,扩大目标硬件资源中,选择FPGA设计(顶级),然后选择包括“MATLAB AXI Master”IP用于基于主机的交互.

在IP核时钟频率(MHz)框,指定IP核时钟频率,单位为MHz。

要确保您的SoC模型支持代码生成,请使用金宝appSoC建设者工具来生成可执行文件并部署模型。有关的更多信息SoC建设者工具,看到生成SoC设计.

有关仅在fpga情况下显示此工作流的示例,请参见导出自定义参考设计.

当SoC模型包含处理器时的额外准备

设备树(DT)是一种向操作系统描述硬件的数据结构。当您向设计中添加IP时,您应该生成一个新的设备树,以便操作系统可以访问该IP。

如果您的模型同时包含FPGA和处理器子系统,那么在导出参考设计之前需要执行这些附加步骤。

2 .在配置参数中,单击硬件实现在左边。然后,扩大目标硬件资源,并选择包括处理系统在FPGA设计(顶级).

运行SoC建设者工具,遵循代码生成的指导步骤,然后将二进制文件加载到FPGA。这一步是必需的,因为SoC建设者自动生成设备树文件(

.dtb)上命名为hdlcoder_rd / soc_prj.output.dtb以及具有匹配设备名称的软件模型。从文件夹中复制设备树文件

hdlcoder_rd保存到SD卡的根文件夹。在生成的plugin_rd.m文件,自定义设备树文件指定为:hRD。DeviceTreeName =“soc_prj.output.dtb”;

执行socExportReferenceDesign函数

属性导出模型的自定义参考设计socExportReferenceDesign函数。例如,对于名为soc_image旋转,在MATLAB中输入此代码®命令提示符。

socExportReferenceDesign(“soc_image_rotation”)

该函数在当前文件夹中生成这些工件。

委员会登记文件

参考设计注册文件

IP存储库

设计文件

约束文件

将IP核集成到生成的参考设计中

将生成的文件夹添加到MATLAB路径中。使用高密度脂蛋白工作流顾问工具来指导您完成集成IP和生成硬件和软件可执行文件的步骤,以便在SoC设备上部署。

有关仅在fpga情况下显示完整工作流的示例,请参见导出自定义参考设计.如果您的模型包含处理系统,则在使用高密度脂蛋白工作流顾问工具。

在Si金宝appmulink中,右键单击要集成到参考设计中的DUT块,并选择HDL代码>高密度脂蛋白工作流顾问打开高密度脂蛋白工作流顾问工具。另外,使用

hdladvisor(高密度脂蛋白编码器)函数。在步骤1.1中,设置目标工作流程来

IP核心代和目标平台生成的平台socExportReferenceDesign函数。点击运行这个任务运行设置目标设备和合成工具的任务。

在步骤1.3中,通过将您的IP中的每个端口连接到参考设计中对应的端口来设置目标接口。

点击运行这个任务运行设置目标接口的任务。

继续执行剩下的步骤高密度脂蛋白工作流顾问工具。

可选:在步骤4.2中,您可以选择生成带有IP核驱动程序块的软件接口模型(需要Embedded Coder)®许可证)。如果您选择生成这个软件界面模型,则清除跳过这个任务下用IP核驱动块生成软件接口模型,用于生成C代码.

有关更多信息,请参阅中“生成软件接口模型”一节瞄准Xilinx Zynq平台(高密度脂蛋白编码器).

生成的软件接口模型包含与DUT子系统接口相匹配的AXI驱动模块。设备名称设置为

“/ dev / mwipcore”默认情况下。更改这些AXI驱动程序块中的设备名称,以匹配SD卡映像使用的设备树文件中的设备名称。有几种方法可以找到设备名称:

设备名称来源于SoC型号的DUT名称。如果您使用指定为DUT名称的SoC模型导出参考设计

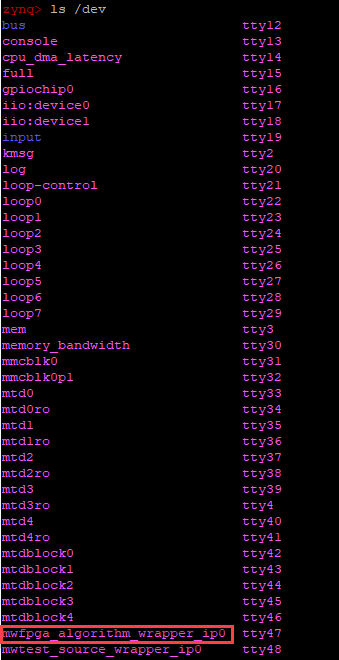

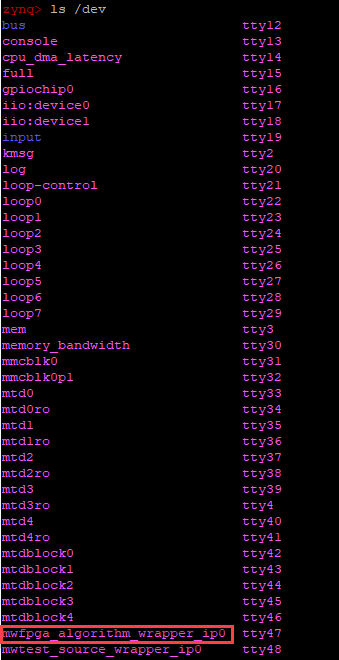

“soc_hwsw_stream_fpga / FPGA算法包装”,则在AXI驱动块中生成的设备名称为“/ dev / mwfpga_algorithm_wrapper_ip0”.在引导SoC设备之后,在操作系统映像中找到设备名称。为此,使用UART或SSH协议登录到主板,并执行:

例如:ls / dev

步骤4.4设置编程方法来下载.

当高密度脂蛋白工作流顾问工具完成构建,它返回生成的位流文件。用生成的比特流文件对FPGA进行编程。

您现在可以在独立模式下部署软件接口模型,或者在外部模式下使用它与SoC设备进行交互。例如,参见“在Zynq ZC702硬件上运行软件接口模型”一节瞄准Xilinx Zynq平台(高密度脂蛋白编码器).

另请参阅

相关的话题

- SoC代工作流

- 自定义参考设计(高密度脂蛋白编码器)

- 导出自定义参考设计

- 开始使用HDL工作流顾问(高密度脂蛋白编码器)