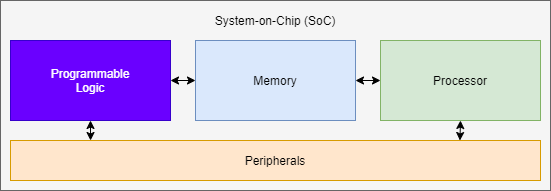

可编程逻辑

为SoC应用程序的可编程逻辑(PL)或FPGA组件设计和开发定制硬件

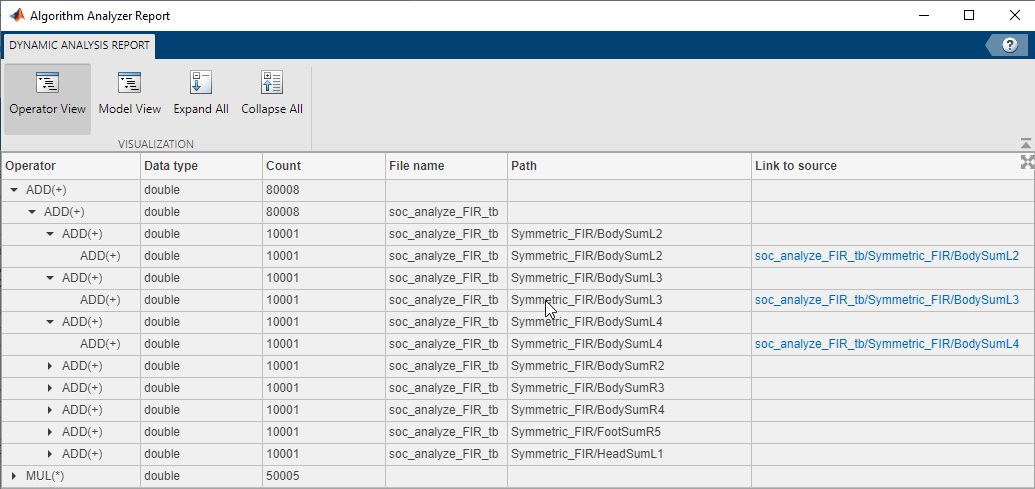

分析Simulink金宝app®通过使用socModelAnalyzer函数来估计模型中使用的资源,比较不同的体系结构,并理解设计权衡。使用socFunctionAnalyzer函数来分析MATLAB中的资源®函数。

的socModelAnalyzer而且socFunctionAnalyzer函数分别创建一个报告,详细说明Simulink模型或MATLAB函数中的操作数量。金宝app

使用报告中的信息:

决定如何将算法划分为软件和硬件。

优化硬件算法。

优化软件算法。

比较一种算法的不同实现,以便对设计选择做出明智的决定。

功能

socModelAnalyzer |

估计操作次数金宝app模型 |

socFunctionAnalyzer |

估计操作次数MATLAB函数 |

socAlgorithmAnalyzerReport |

开放算法分析报告 |

socExportReferenceDesign |

导出自定义参考设计HDL工作流顾问 |

工具

| 逻辑分析仪 | 随着时间的推移,可视化、测量和分析转换和状态 |

金宝appSimulink配置参数

主题

当您的FPGA模型包含多个您希望使用HDL Coder™为其生成HDL的块时,您必须使用连接器模型来连接您的块。

控件生成的报告的详细信息socModelAnalyzer或socFunctionAnalyzer函数。

使用socExportReferenceDesign功能,从SoC Blockset™模型导出自定义参考设计。

故障排除

在生金宝app成SoC设计时使用不支持的模式SoC建设者.