项目独立赛灵思公司FPGA开发板金宝app

这个例子展示了如何将Xilinx作为目标®FPGA开发板采用FPGA Turnkey工作流程进行综合。

的hdlcoderUARTServoControllerExampleXilinx模型被设计用于使用Xilinx Virtex®-5 ML506开发板。的UART_Servo_on_FPGA子系统通过UART端口接收命令。该子系统产生一个脉宽调制(PWM)波形来控制伺服电机。

在你开始之前

要运行此示例,必须设置合成工具。要学习如何设置合成工具,请参见合成刀具路径设置.

本例使用Xilinx Virtex-5 ML506开发板。您可以在不同的板上尝试这个示例,并根据该板的接口定义指定目标接口。要查看FPGA Turnkey工作流支持的板列表金宝app,请参见金宝app支持EDA工具和硬件.

如果要下载编程文件,必须先连接目标设备。但是,如果目标设备没有连接,您仍然可以生成编程文件。

打开模型

将示例目录添加到MATLAB中®路径。

目录(fullfile (docroot,“工具箱”,“hdlcoder”,“示例”))

打开模型。

hdlcoderUARTServoControllerExampleXilinx

选择目标设备

右键单击

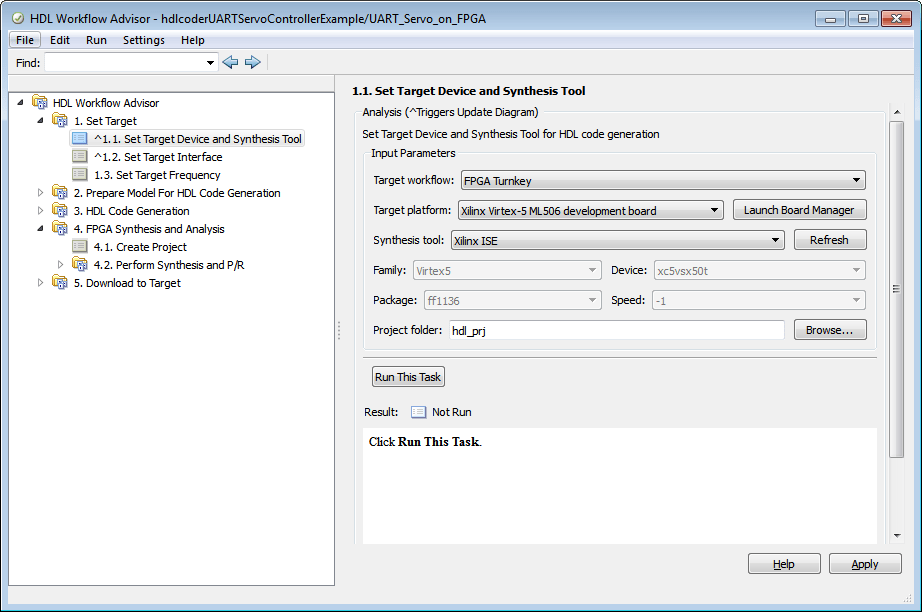

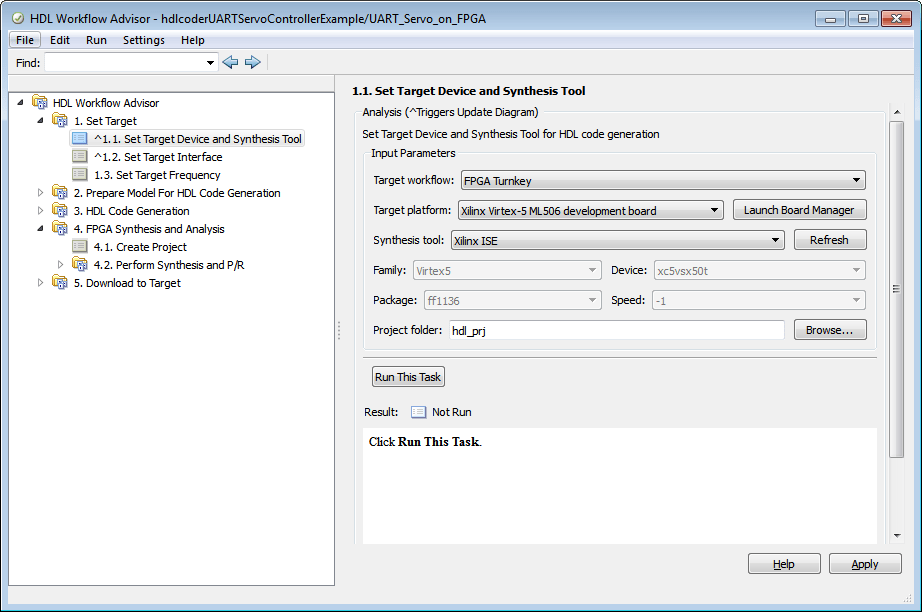

UART_Servo_on_FPGA子系统和选择HDL代码>高密度脂蛋白工作流顾问.在HDL Workflow Advisor中,选择设定目标>设置目标设备和合成工具的任务。

为目标工作流程中,选择FPGA交钥匙.

为目标平台中,选择Xilinx Virtex-5 ML506开发板.

如果单板没有自动出现在列表中,请选择得到更多的董事会下载Xilinx FPGA Boards支持包。金宝app

HDL工作流顾问会根据您的电路板选择自动设置合成工具。

点击运行这个任务.

设置目标界面和目标频率

在HDL Workflow Advisor的左窗格中,选择设置目标接口的任务。

控件中为每个端口选择一个选项目标平台的接口菜单如下图所示,单击应用.

每个端口被分配到指定的位位置

[或位位置的范围b][.规格的宽度,以位为单位,必须等于DUT上端口的宽度。当您选择选项时,HDL Workflow Advisor会自动分配一个位范围。可以双击位范围/地址/ FPGA引脚列编辑值。lsb:最高有效位]查阅每一项的详细资料目标平台的接口选项,请参阅Xilinx Virtex-5 ML506开发板文档。

请注意

您必须为目标设备分配至少一个输出端口。如果不分配端口,则设置目标接口任务显示错误并终止。

点击运行这个任务.

在设置目标频率任务,设置FPGA系统时钟频率到100兆赫,然后单击运行这个任务.

在本例中,由于UART波特率固定,目标频率必须设置为100MHz(默认值)。

生成代码,合成和程序目标设备

在选择目标设备并配置其端口接口后,HDL Workflow Advisor可以自动执行下一个任务序列。这些任务包括:

为HDL代码生成准备模型:检查模型的HDL代码生成兼容性。

HDL代码生成:设置“模型配置参数”对话框中与HDL相关的选项并生成HDL代码。

FPGA综合与分析:在Xilinx ISE中执行综合和时序分析。利用合成过程中获得的关键路径信息对模型进行反向标注。

下载到目标有两个子任务:

生成编程文件:生成FPGA编程文件。

项目目标设备:下载程序文件到单板。

提示

在执行之前项目目标设备任务,确保您的主机通过JTAG编程电缆正确地连接到Xilinx Virtex-5 ML506开发板。

要自动运行以下任务序列:

打开下载到目标任务组。

右键单击项目目标设备并选择运行到选定任务.

任务序列通过使用生成的编程文件对目标板进行编程而结束。然后可以读取代码生成和合成日志文件。