FPGA编程和在SpeedGoat Simulink可编程I / O模块上的配置金宝app

这个例子展示了如何使用HDL Workflow Advisor在Speedg金宝appoat的Simulink可编程I/O模块上实现Simulink®算法。你跑的金宝appSimulink实时FPGA IO工作流程:

指定FPGA I/O模块及其接口。

合成FPGA编程的Simuli金宝appnk算法。

生成Simulink®金宝app实时™接口子系统模型。

接口子系统模型包含对FPGA进行编程的模块,并在实时应用程序执行期间通过PCIe总线与FPGA模块进行通信。将生成的子系统添加到Simulink Real-Time域模型中。金宝app

此示例使用SpeedGoat IO397-50K模块。看SpeedGoat FPGA支金宝app持HDL工作流程顾问.

设置和配置

在将算法部署在SpeedGoat IO模块上之前:

1.安装最新版本的Xilinx®Vivado®HDL语言支持和支持的第三金宝app方工具和硬件.

然后,将刀具路径设置为已安装的Xilinx Vivado可执行文件可执行文件hdlsetuptoolpath功能。

hdlsetuptoolpath ('toolname'那“Xilinx Vivado”那“路径”那'C:\ Xilinx \ Vivado \ 2019.2 \ Bin \ Vivado.bat'的)

2.对于实时仿真,请设置开发环境和目标计算机设置。看立即开始使用Simulink金宝app(金宝app实时仿真软件).

3.安装SpeedGoat库和SpeedGoat HDL编码器集成包。看安装SpeedGoat HDL编码器集成包.

高密度脂蛋白工作流顾问

HDL工作流程顾问通过HDL代码生成和FPGA设计过程指导您。使用顾问:

检查HDL代码生成兼容性的型号并修复不兼容的设置。

生成HDL代码、测试平台和脚本,以构建和运行代码和测试平台。

进行合成和定时分析。

将生成的代码部署到soc、fpga和Speedgoat I/O模块上。

要打开模型内的子系统的HDL工作流程顾问,请使用HDLadvisor.功能。

load_system('sschdlextwolevelconverterigbtexample')HDLadvisor('sschdlextwolevelconverterigbtexample / simscape_system'的)

Advisor的左窗格包含代表一组相关任务的文件夹。展开文件夹并选择任务将在右侧窗格中显示有关该任务的信息。右窗格包含一些简单的控件,用于将任务运行到控制HDL代码和测试台生成的高级参数和选项设置。要了解关于每个任务的更多信息,右键单击该任务并选择这是什么?.看开始使用HDL工作流顾问.

金宝appSimulink环回域模型

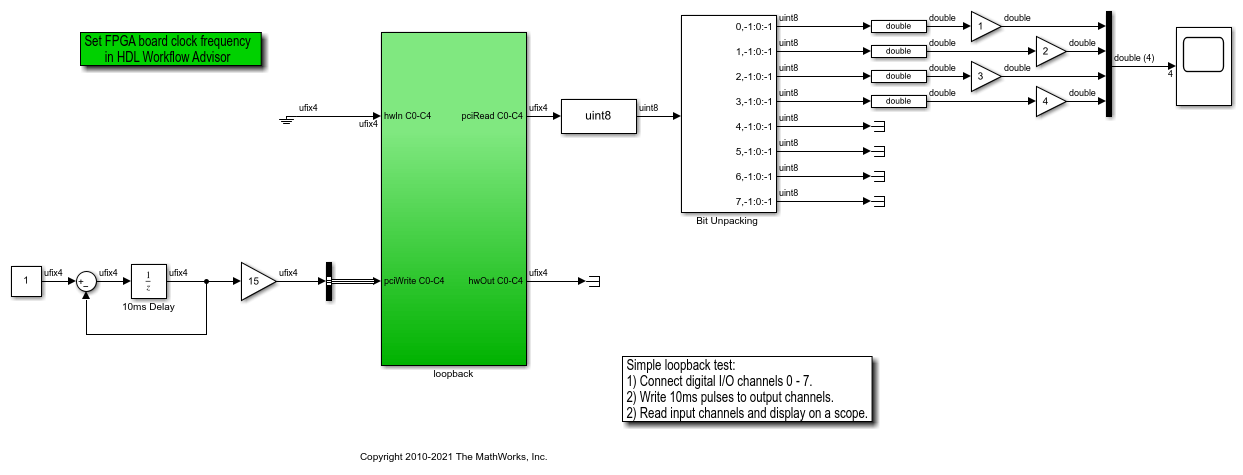

Simu金宝applink域模型具有包含在FPGA芯片上的算法的子系统。在将算法下载到FPGA板之前,使用此模型在仿真环境中测试您的FPGA算法。在这种情况下,该模型是环回测试。

open_system (“dslrtSGFPGAloopback_fpga”的)

此模型是FPGA域模型。它表示FPGA板上时钟的模拟采样率。的回送子系统包含要在FPGA上加载的算法。模型的数据类型和输入和输出行的数量配置为适合speedgoat io397-50k.平台。

open_system (“hdlcoder_slrt_loopback”)set_param(“hdlcoder_slrt_loopback”那'simulationcommand'那'更新'的)

生成Speedgo金宝appat IO397平台的Simulink实时接口模型

1.打开HDL工作流程顾问回送子系统。该子系统已加载到FPGA上。

hdladvisor ('hdlcoder_slrt_loopback / loopback'的)

2.扩展设定目标文件夹中。在里面设置目标设备和合成工具任务,指定目标工作流程作为金宝appSimulink实时FPGA I / O.和目标平台作为speedgoat io397-50k..右键单击设定目标参考设计任务和选择运行到选定任务.

3.在里面设置目标界面任务,地图端口HWIN.和huout.到IO397_TTL [0:13]和pciRead C0-C4和PCIWRITE C0-C4到PCIe接口.点击运行此任务.

4.运行设置目标频率任务的默认值设置为目标频率(MHz).目标频率必须在范围内频率范围(MHz).

5.扩大下载到目标的任务。右键单击生成Simulin金宝appk实时界面任务和选择运行到选定任务.

此任务生成RTL代码和IP核心,FPGA比特流和Simulink实时界面模型。金宝app在里面创建项目任务,打开Vivado项目查看实现的块设计。

实时子系统集成和执行

之后生成Simulin金宝appk实时界面任务通过,单击链接以打开Simulink实时界面模型。金宝app

Simu金宝applink- real Time Interface模型包含一个与Simulink FPGA域模型中的子系统同名的掩码子系统。该子系统是Simulink Real-Tim金宝appe Interface子系统,其中包含加载到FPGA上的算法。使用生成的Simulink Real金宝app-Time Interface模型或创建一个Simulink Real-Time Domain模型,并将Simulink Real-Time Interface子系统复制到该模型中,以便在Speedgoat目标机器上模拟您的FPGA算法。

在Simuli金宝appnk Real-Time接口子系统掩码中,设置三个参数:

设备索引

PCI插槽

采样时间

当目标有一个FPGA I / O板时,将设备索引留给默认值。对于多个FPGA I / O板,请指定唯一的设备索引。如果两个或多个电路板具有相同类型,请为每个板指定PCI插槽。

对于实时测试,您可以在仿真数据检查器上记录信号并查看仿真结果。

在这方面实时选项卡,打开Simulink金宝app实时资源管理器并指定目标接口连接设置。例如,看到SpeedGoat FPGA I / O模块上Simsce Model的硬件循环实现.

在这方面实时选项卡,单击在目标上运行构建和下载Simulink实时应用程序。金宝app实时应用程序加载到Speedgoat目标机器上,FPGA算法比特流加载到FPGA上。

然后,您可以在仿真数据检查器上查看模拟结果。