用MATLAB进行FPGA设计,第1部分:为什么要使用MATLAB和Simulink金宝app

从系列中:基于MATLAB的FPGA设计

Raghu Sivakumar,MathWorks

HDL编码器™ 生成可合成的VHDL®或Verilog®MATLAB中的RTL®函数,Simulink金宝app®模型和状态流®可用于针对FPGA或ASIC硬件的图表。本教程使用一个简单的信号处理算法来展示我们的客户遵循的典型步骤,以根据硬件体系结构细节调整他们的高级算法,从而可以在硬件中高效地实现这些算法,并在每个步骤中进行验证。

本视频包括:

- 硬件设计的关键考虑因素:流数据和固定资源

- MATLAB和Simulink的优势以及如何利用金宝app它们进行硬件设计

- 工作流程概述,包括每个步骤的验证

- HDL编码器自导教程概述

- MATLAB黄金参考算法简介

- 使基于帧的算法适应流式算法

欢迎来到HDL编码器视频系列。在本系列视频中,我们将学习一种流行的、经过验证的生产方法,即使用MATLAB数字信号处理算法通过Simulink、定点设计器和HDL编码器以FPGA为目标。金宝app

在视频系列的第一部分中,我们将讨论MATLAB和Simulink的优势,并概述MathWorks文件交换网站上提供的HDL编码器自导教程。金宝app

HDL编码器从MATLAB函数、Simulink模型和状态流程图生成可合成的VHDL或Verilog,这些可用于针对FPGA或ASIC硬件。金宝app

MATLAB是一种高级语言和交互式环境,在这种环境中,可以轻松地对大型数据集执行复杂的数学运算。MATLAB的这种能力使其成为开发数字信号处理算法的理想工具。为了将如此强大的语言应用于硬件,我们需要了解FPGA硬件是一组固定的资源。FPGA硬件具有有限的资源带宽,包括输入/输出块、内存和DSP片,必须有效地使用这些资源来实现优化设计架构,同时实现预期结果。由于资源在硬件中是固定的,为了在大型数据集上执行操作,我们将在比特流上工作,同时协调时间以获得正确答案。

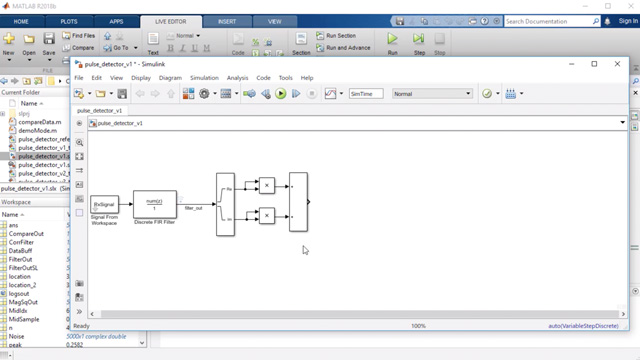

金宝appSimulink提供了一个环境,在该环境中,您可以描述算法设计如何与数据流协同工作,并在转移到硬件实现之前进行模拟。Simulink具有内置的时间感,有助于可视化数据类型和大小,以及通过操作进行传播,这些是创建良好硬件体系结构的关键。Simulink有一个HDL优化库,具有250多个块,并与HDL代码生成兼容。

因此,要在FPGA上部署MATLAB算法,推荐的工作流程是将MATLAB和Simulink结合起来,在仿真环境中结合文本和图形编程。我们将使用MATLAB算法作为黄金参考,在Sim金宝appulink中描述硬件架构,转换为定点,并利用Simulink的可视化优化生成的HDL代码。因此,Simulink中的每个步骤都可以在MATLAB中进行验证,并利用MATLAB作为测试和可视化环境。

为了说明工作流程,我们将利用MathWorks文件交换网站上的HDL编码器自助教程示例。

本教程附带了一个可视指南,并提供了在FPGA上实现MATLAB算法的分步说明。此外,本教程还提供了必要的MATLAB和测试台脚本。

在MATLAB参考脚本中,创建要检测的脉冲,并将其插入传输信号中。添加噪波以表示真实世界的接收信号。为了在MATLAB中检测脉冲,我们将利用接收信号的整个“帧”,并将其通过具有所需系数的匹配滤波器。该算法将成为我们的MATLAB黄金参考,它将检测峰值及其位置。

硬件工作在连续的比特流上,峰值检测是通过在比特流样本上滑动窗口来实现的。为了确保这种方法能给出预期的结果,我们创建了一个代表硬件实现的MATLAB算法。我们称之为硬件友好算法。

硬件实现算法在标准下检测最后11个样本的滑动窗口内的峰值。中间样本最大,且中间样本大于预定阈值。该算法将用于验证和比较Simulink模型实现的输出。金宝app

在关于HDL编码器的本系列视频的第一部分中,我们讨论了MATLAB和Simulink环境的优势,并概述了脉冲检测器MATLAB算法,该算法将用于强调在FPGA上实现MATLAB算法所需的HDL编码器工作流程金宝app。

在下一个视频中,我们将设计脉冲检测器算法的Simulink实现,并将其与M金宝appATLAB golden reference进行比较。

您还可以从以下列表中选择网站:

如何获得最佳的站点性能

选择中国站点(中文或英文)以获得最佳站点性能。其他MathWorks国家/地区网站未针对您所在地的访问进行优化。