基于MATLAB命令的实时数据硬件原型FPGA设计

这个例子展示了如何使用MATLAB从你的主机在FPGA硬件上运行一个算法原型。

介绍

在设计过程的许多阶段,与直接在硬件上运行的FPGA设计进行交互是很有用的。与硬件一起工作使您能够快速原型设计,验证功能,调整关键参数,连接到真实世界的信号,收集数据进行分析,等等。

这个示例向您展示了如何将主机上的MATLAB连接到FPGA硬件。用MATLAB来:

将输入信号写入FPGA算法。

从FPGA捕获输出信号进行分析。

在FPGA设计中读取和写入寄存器。

作为这个例子的一部分,你:

在硬件上生成和部署一个简单的算法。

创建硬件对象以建立到FPGA的连接。

使用一个简单的脚本原型设计运行在硬件和实时数据。

在你开始之前

要运行此示例,请安装和设置:

用于Xilinx Z金宝appynq平台的HDL编码器支持包

Xilinx Vivado的版本金宝app支持的第三方工具和硬件)

Xilinx SoC。这个例子使用了ZedBoard。

主板SD卡上的MathWorks固件图像。有关SD卡设置的帮助,请参见SD卡引导安装(Xilinx Zyn金宝appq平台的HDL编码器支持包)。

系统架构

前面的图像显示了系统的高级体系结构。上位机通过SoC (system on Chip)板上的处理系统与FPGA通信。主机可以发送和接收数据帧,这些数据帧通过直接存储器访问(DMA) ip转换为流数据。主机还可以通过写入算法IP核中的AXI4-Lite寄存器来优化参数。

FPGA算法

部署在FPGA上的算法是一个简单的流算法,它将输入信号的振幅按一个常数缩放。流数据是用数据和有效信号建模的。振幅信号被建模为一个常数。

打开模型。该模型由被测设计(DUT)和试验台组成。DUT包含部署在FPGA上的算法。测试台在模拟期间通过提供输入和捕获输出以供显示来练习DUT。

% open_system hdlcoder_scale_amplitude.slx

生成HDL IP核

使用HDL Workflow Advisor从DUT生成IP核:

1.在MATLAB命令窗口中使用以下命令设置Xilinx Vivado合成工具路径。运行该命令时,请使用您自己的Vivado安装路径。

hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,“C: \ Xilinx \ Vivado \ 2020.1 \ bin \ vivado.bat ');

2.打开HDL Coder工具条应用程序> HDL编码器.单击工具条图标以打开Workflow Advisor。

3.在设置目标设备和合成工具任务,选择IP核心代为目标工作流程和ZedBoard为目标平台.如果您的目标是不同的Xilinx SoC,请从Target平台上下文菜单中选择您的板。

点击运行这个任务.

4.在设定目标参考设计任务,选择带有AXI4-Stream接口的默认系统为参考设计.

点击运行这个任务。

5.在设置目标接口任务的端口DUT子系统映射到IP Core接口。将输入数据和有效端口映射到AXI4-Stream奴隶.将输出数据和有效端口映射到AXI4-Stream主.振幅信号被映射到AXI4-Lite.

点击运行这个任务.

6)右键单击生成RTL代码和IP核任务,并选择运行到选定任务生成IP核。

生成主机和IP核之间的接口

要生成IP核的主机接口,并将设计部署到目标硬件板:

1.运行创建项目的任务。该任务将为FPGA算法生成的IP核插入到参考设计中,以创建系统架构图中所示的系统。

2.在生成软件界面任务,选择对应的框生成MATLAB软件界面脚本然后运行此任务。

3.两个MATLAB文件生成在您的当前文件夹,使您可以原型您生成的IP核直接从MATLAB。

4.检查这些生成的文件与上位机FPGA设计交互。首先,完成剩下的Workflow Advisor任务。运行构建FPGA比特流任务,可能需要一些时间才能完成。

5.运行项目目标设备任务将FPGA算法编程到板上。选择下载将FPGA位流下载到SD卡上,配置ARM处理系统正常启动。

与上位机FPGA设计交互

在上位机上通过MATLAB读写数据与FPGA设计交互。

打开生成的脚本文件:

开放gs_hdlcoder_scale_amplitude_interface.m

此文件创建到FPGA硬件的连接,用于读写数据。

创建一个“fpga”硬件对象,它表示到硬件板上的fpga的连接。

使用您的DUT算法所需的硬件接口和端口配置“fpga”对象。

读取和写入数据到DUT端口,以锻炼您的算法在硬件上运行。

释放所有硬件资源

fpga对象来清除连接。

打开生成的setup函数:

开放gs_hdlcoder_scale_amplitude_interface.m

本功能用于配置fpga属性中映射的具有相同端口和接口的硬件对象设置目标接口的任务。您可以重用这个函数,可以在您自己的脚本中重新创建这个配置。

您可以修改生成的脚本文件来练习算法在硬件上的运行。一个活动脚本已经准备好了,你可以通过运行下面的命令打开它:

开放hdlcoder_scale_amplitude_script.mlx

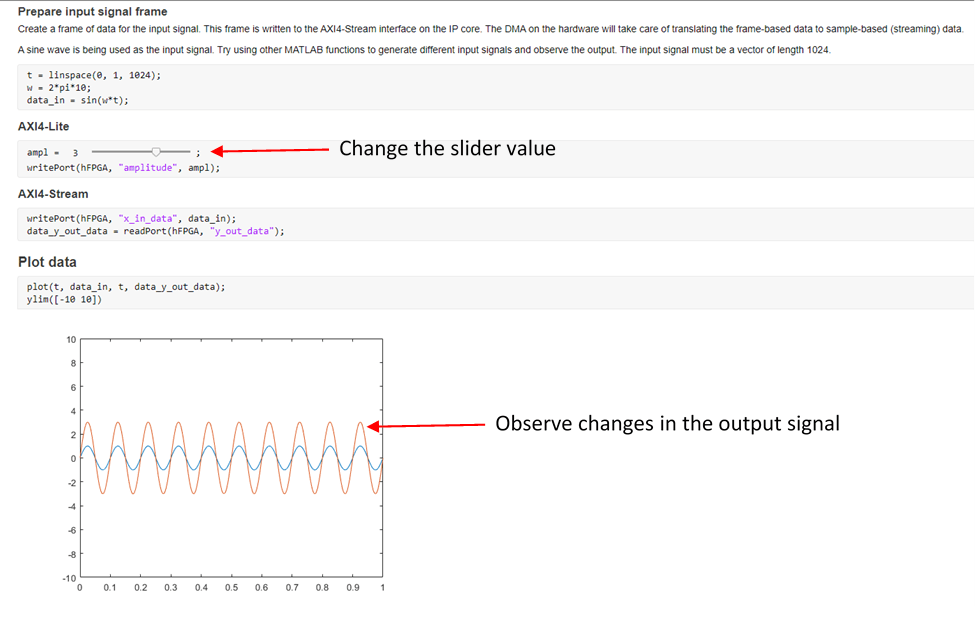

更改滑块的值并观察输出数据(橙色)在其下面的图表中如何变化。当滑块移动时,它下面的代码将被执行。代码的每次执行:

将新的振幅值从滑块写入IP核中的AXI寄存器。

写入输入信号的一帧。

读取一帧输出信号。

将输入和输出信号绘制在同一个图形上,以显示振幅的差异。

完成后,运行脚本的最后一行以释放fpga清理对象:

释放(hFPGA);

下一个步骤

进一步实验生成的脚本: