使用FPGA数据捕获调试IP核心

此示例显示了如何使用HDL验证者的FPGA数据捕获功能调试HDL编码器生成IP核心。

要求

Xilinx Zynq ZC702评估套件

Xilinx Zyn金宝appq平台的HDL编码器支持包

Xilinx FPGA板的金宝appHDL验证支持包

(可选)Xilinx Zynq平台的嵌入式编码器支持金宝app包

(可选)DSP系统工具箱

请按照HDL编码器示例中的“设置Zynq硬件和工具”部分开始定位Xilinx Zynq平台(HDL编码器)设置ZC702硬件。

介绍

当您从HDL编码器调试生成的IP核心时,在实际硬件上运行时,监视IP核心内部信号是很有用的。此示例显示了如何使用HDL验证者的FPGA数据捕获将这些信号捕获到MATLAB中进行调试分析。

首先查看示例模型:

open_system('hdlcoder_led_blinking_data_capture');

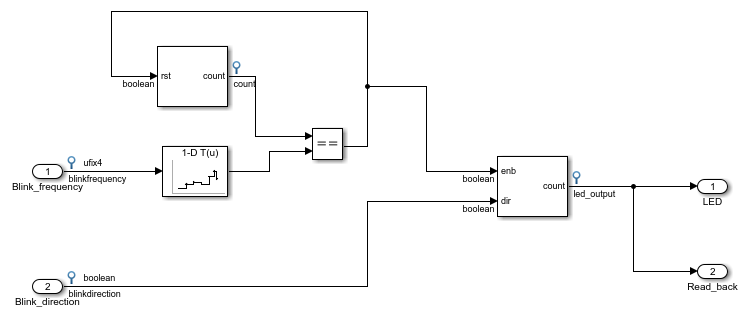

子系统LED_Counter是针对FPGA面料的硬件子系统。在该子系统内部,我们将几个内部信号标记为测试点。HDL编码器将将这些内部信号从DUT和IP核心包装器中路由,以便可以将信号连接到FPGA数据捕获HDL IP。

open_system('HDLCODER_LED_BLINKING_DATA_CAPTURE/LED_COUNTR');

生成HDL IP核心

从模型启动HDL工作流顾问,并通过IP核心生成工作流程运行。有关详细的逐步指南,请参阅该示例开始定位Xilinx Zynq平台(HDL编码器)

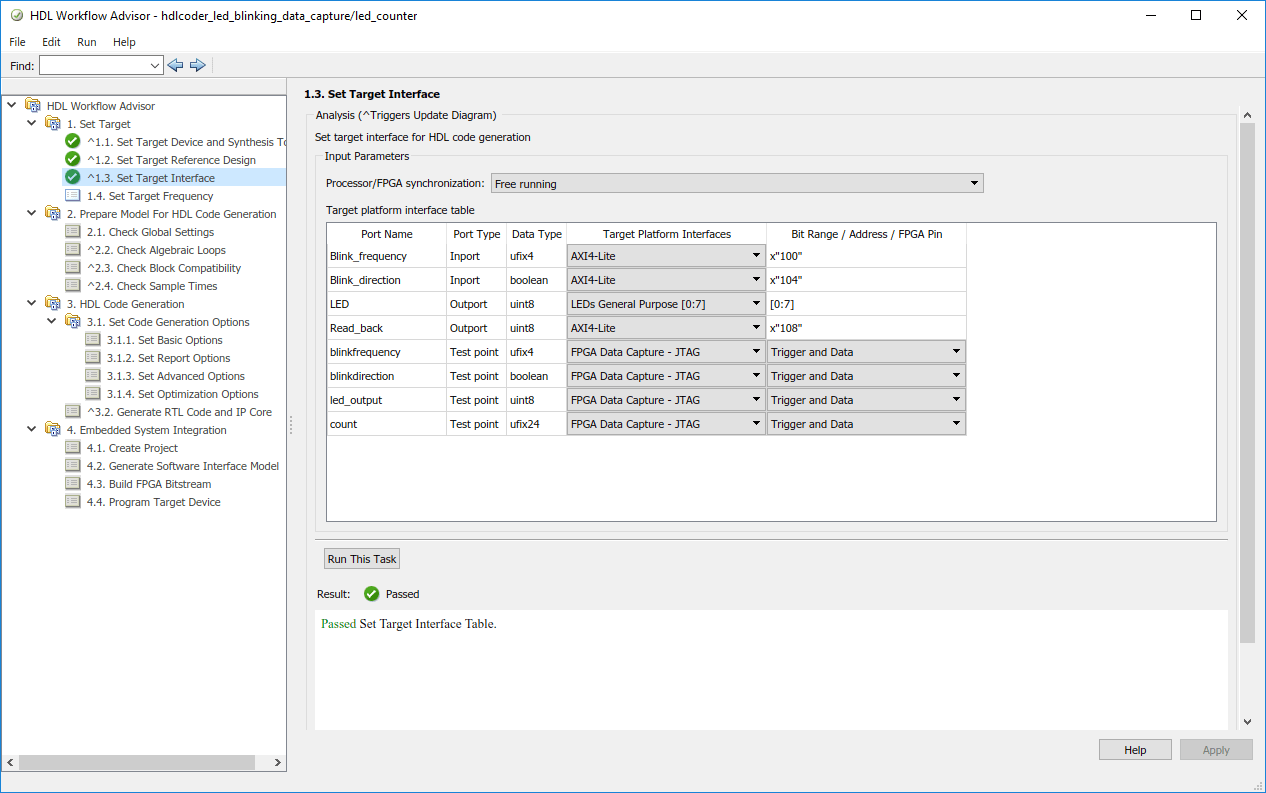

1。在步骤1.1中,选择目标工作流中的IP核心生成。对于“目标平台”,选择“ Xilinx Zynq ZC702评估套件”

2。在步骤3.1.3中,在“端口”选项卡下检查“启用HDL DUT端口生成测试点”

3。在步骤1.3中,选择“ FPGA数据捕获-JTAG”接口,用于BLINKFREQUENCY,BLINKDIRECTION,LED_OUTPUT和计数端口。

4。通过其余的工作流步骤运行以生成HDL IP,并编程目标设备。

从IP核心捕获和显示数据

现在已经对FPGA面料进行了编程和运行,下一步是从Zynq板上捕获数据。

首先,找到FPGA数据捕获启动脚本。在此示例中,该脚本在您的HDL代码生成目录中:HDL_PRJ/ip_core/led_count_ip_v1_0/fpga_data_capture/lunageDataCaptureApp.m。您还可以在代码生成报告中找到此脚本。

接下来,在MATLAB中运行此脚本。您将需要添加此脚本位于MATLAB路径的目录或更改当前文件夹。

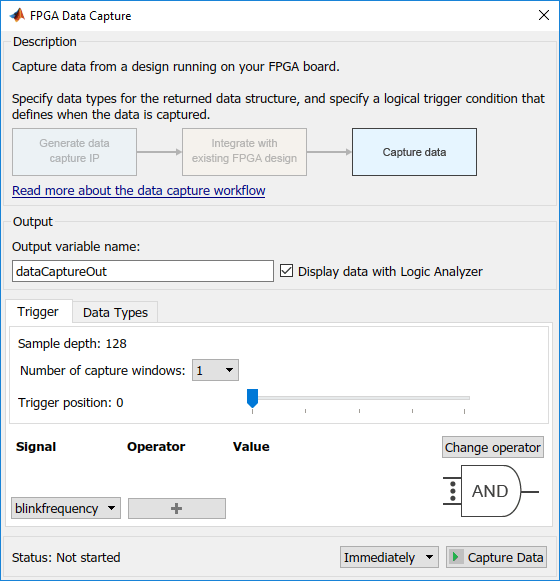

执行此脚本后,启动了FPGA数据捕获应用程序。您可以单击“捕获数据”按钮以捕获FPGA的数据,而无需设置任何触发器。

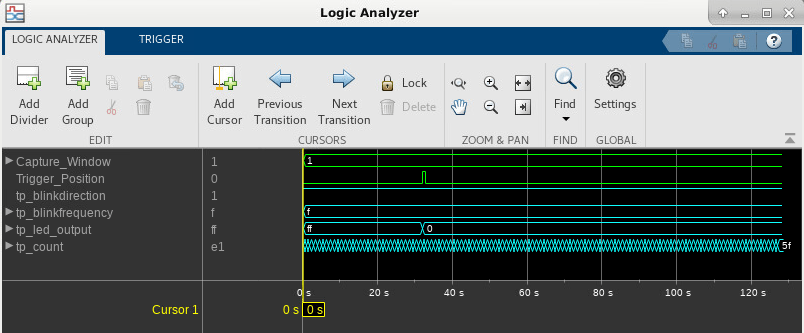

另外,您可以设置一个触发条件,其中led_counter == 0,然后触发32的位置。然后再次单击“捕获数据”按钮。