验证了用fpga在环实现PID控制器的HDL实现

这个示例向您展示了如何使用HDL验证器™设置fpga在环(FIL)应用程序。该应用程序使用Simulink®和FPGA金宝app开发板验证比例-积分-微分(PID)控制器的HDL实现。在本例中,Simulink生成电机金宝app的期望位置,并仿真由该PID控制器控制的电机。

要求和先决条件

除了列出的MathWorks产品外,其他要求包括:下载188bet金宝搏

FPGA设计软件(Xilinx®ISE®设计套件,或Xilinx®Vivado®设计套件,或Intel®Quartus®II设计软件,或Microsemi®Libero®SoC设计软件)

其中一个金宝app支持的FPGA开发板和配件

使用以太网连接:主机上安装的千兆以太网适配器、千兆以太网交叉网线

有关使用JTAG的连接:USB Blaster I或II电缆和INTEL FPGA板的驱动程序。Digilent®JTAG电缆和Xilinx FPGA板的驱动器。

有关使用PCIExpress®的连接:FPGA板安装到主机的PCI Express插槽中。

先决条件:

MATLAB®和FPGA设计软件可以本地安装在您的计算机上或在网络可访问的设备上。如果使用来自网络的软件,则需要在计算机中安装第二个网络适配器,以便为FPGA开发板提供专用网络。请参阅计算机的硬件和网络指南,了解如何安装网络适配器。

第1步:设置FPGA开发板

跳过此步骤,如果您使用PCI Express连接进行仿真,请执行步骤2。如果尚未设置PCI Express连接,请使用“支持包安装软件”来指导您完成PCI Express Setup。金宝app

使用以下步骤设置FPGA开发板。

确保电源开关保持不变从。

将交流电源线连接到电源插头。将电源适配器电缆插入FPGA开发板。

使用交叉网线将FPGA开发板上的以太网连接器直接连接到计算机上的以太网适配器。

使用JTAG下载电缆将FPGA开发板与计算机连接。

确保FPGA开发板上的所有跳线都处于出厂默认位置,Microsemi PolarFire除外,需要特殊设置。看到安装MicroSemi北极火评估套件(Microsemi FPG金宝appA板的HDL验证器支持包)。

第2步:设置主机计算机板连接

如果使用JTAG连接进行模拟,请跳过此步骤。要使用以太网连接,您的计算机上必须有一个千兆以太网网络适配器才能运行此示例。

在Windows®上,执行以下步骤:

打开控制面板。

类型查看网络连接在搜索栏中。选择查看网络连接在搜索结果中。

右键单击到FPGA开发板的连接图标并选择属性从弹出菜单中。

在下面此连接使用以下项目, 选择Internet协议版本4(TCP / IPv4)并点击属性。

选择请使用以下IP地址:。放IP地址到192.168.0.1。如果您的网络上另一台计算机使用此地址,请将其更改为此子网上的任何可用IP地址,例如192.168.0.100。这是您的主机地址。设定子网掩码到255.255.255.0。现在,您的TCP / IP属性如下图所示:

在Linux®上:

使用ifconfig命令设置本地地址。例如:

% ifconfig eth1 192.168.0.1

在此示例中,ETH1是Linux计算机上的第二个以太网适配器。检查您的系统,以确定哪些以太网适配器已连接到FPGA开发板。上面的命令将本地IP地址设置为192.168.0.1。如果您的网络上另一台计算机使用此地址,请将其更改为此子网上的任何可用IP地址,例如192.168.0.100。

第3步:准备示例资源

1.设置FPGA设计软件

在使用FPGA循环之前,请设置系统环境以访问FPGA设计软件。您可以使用该功能hdlsetuptoolpath将ISE,Vivado,Quartus或Libero Soc添加到当前MATLAB会话的系统路径中。下面给出每个工具的示例命令行。如果不同,请使用实际的可执行文件替换。

对于使用ISE设计软件的Xilinx FPGA板,运行:

hdlsetuptoolpath (“ToolName”那'Xilinx Ise'那'工具路径'那'c:\ xilinx \ 13.1 \ ise_ds \ ise \ bin \ nt64 \ ise.exe');

对于使用Vivado设计软件的Xilinx FPGA板,运行:

hdlsetuptoolpath (“ToolName”那'Xilinx Vivado'那'工具路径'那“C: \ Xilinx \ Vivado \ 2016.4 \ bin \ vivado.bat ');

对于Intel板,运行:

hdlsetuptoolpath (“ToolName”那'Altera Quartus II'那'工具路径'那“C: \ \ 16.0 \负责第四的\ bin \ quartus.exe ');

对于Microsemi板,运行:

hdlsetuptoolpath (“ToolName”那Microsemi自由人SoC的那'工具路径'那“C: \ Microsemi \ Libero_SoC_v11.8 \设计\ bin \ libero.exe”);

2.打开fil_pid模型。

该模型包含一个使用基本Simulink块实现的固定点PID控制器。金宝app该模型还包含由该PID控制器控制的直流电机模型以及所需的直流电机位置作为输入刺激。

现在运行这个模型,观察电机在范围内的期望和实际位置。

第4步:启动FPGA-IN-in-Loop(FIL)向导

通过执行以下操作,启动FPGA-In-Loole向导:

打开应用画廊和选择FIL巫师从代码验证,验证和测试部分。

或者,您可以在MATLAB命令提示符下输入FILWIZARD命令。

filWizard

第5步:在FIL向导中指定硬件选项

设置FPGA开发板的FIL选项。

1.指定向导将生成FIL Simulink块还是FILSimulation MATLAB金宝app系统对象。对于本例,请选择金宝app为FIL模拟金宝app仿真软件。

2.为董事会名称,选择连接到主计算机的FPGA开发板。如果您的电路板不在列表中,请选择以下选项之一:

“获取更多电路板...”以下载FPGA板支持包(此选项启动支持包安装程序)。金宝app

“创建自定义板......”为特定FPGA板创建FPGA板定义文件(此选项启动新的FPGA板管理器)。

3.选择要模拟的连接。可用的连接方法是以太网和JTAG。并非所有板都支持两个连接方法。金宝app

4.仅限以太网连接:如果您从192.168.0.x更改了计算机的IP地址,请从192.168.0.x设置网络适配器时,或者如果默认电路板IP地址192.168.0.2正在使用其他设备,则展开高级选项并改变董事会的IP地址根据以下指导方针:

子网地址,通常是电路板IP地址的前三个字节,必须与主机IP地址相同。

单板IP地址的最后一个字节不能和主机IP地址的最后一个字节相同。

单板的IP地址不能与其他计算机的IP地址冲突。

例如,如果主机IP地址为192.168.8.2,则可以使用192.168.8.3如果可用。不要换董事会MAC地址。

5.可选:如果您想从默认(25MHz)更改DUT时钟频率,则可以扩展高级选项并改变FPGA系统时钟频率(MHz)。

6.点击下一个接着说。

步骤6:在FIL向导中指定HDL文件

指定要在FPGA中实现的HDL设计。

1.单击“添加”并浏览到您在准备示例资源中创建的目录。

2.在PID_HDLSRC目录中选择这些HDL文件:

Controller.VHD.

d_component.vhd.

i_component.vhd.

这些是在FPGA板上验证的HDL设计文件。

3.在源文件表,请选中文件行上的复选框Controller.VHD.以指定该HDL文件包含顶级HDL模块。

FIL向导会自动填充顶级模块名称字段与所选HDL文件的名称;在这种情况下,控制器。在此示例中,顶级模块名称与文件名匹配,以便您无需更改它。如果顶级模块名称和文件名不匹配,则会在此对话框中手动更正顶级模块名称。

点击下一个接着说。

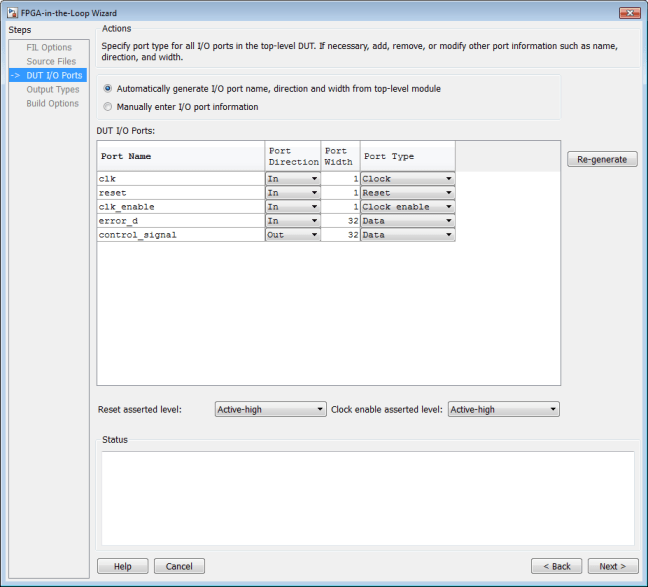

第7步:在FIL向导中查看I / O端口

FIL向导解析了Controller.VHD中的顶级HDL模块控制器,以获取所有I / O端口并在DUT中显示它们I / O端口桌子。解析器尝试通过查看端口名称自动确定可能的端口类型,并在端口类型下显示这些信号。

1.检查港口倾斜。如果解析器为任何给定端口分配了不正确的端口类型,您可以手动更改信号。对于同步设计,指定一个时钟、复位或时钟使能信号。在本例中,FIL向导会自动正确地填充表。

2.点击下一个接着说。

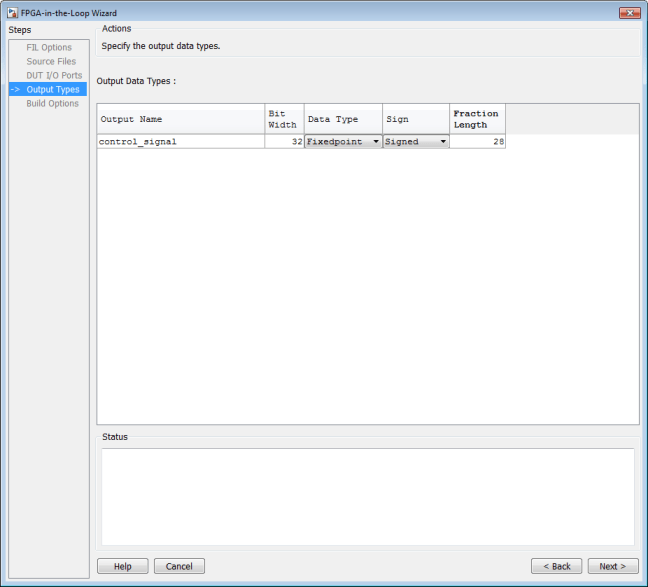

第8步:在FIL向导中设置输出数据类型

1.对于HDL输出control_signal改变数据类型到定点那标志到签和分数长度到28.。这将使生成的FIL块将FPGA设计欠款(DUT)的输出信号设置为正确的数据类型。

2.点击下一个接着说。

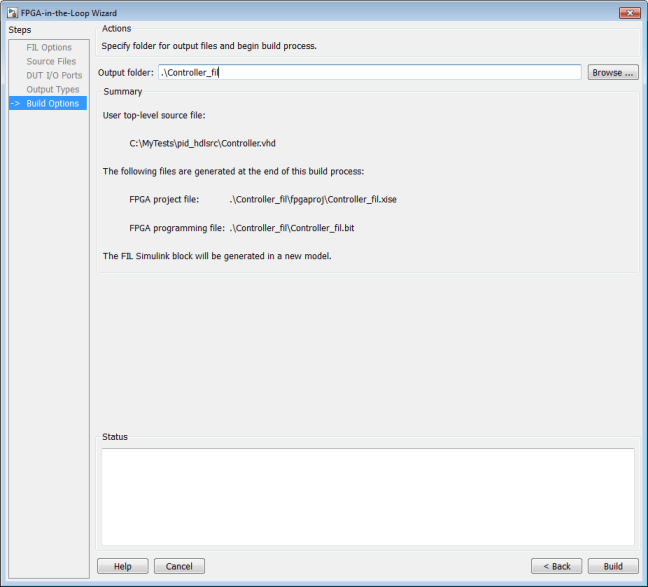

步骤9:在FIL向导中查看构建选项

1.指定输出文件的文件夹。对于本例,使用默认选项,它是一个名为controller_fil.在当前目录下。

这概括显示FPGA项目文件和FPGA编程文件的位置。您可能需要这两个文件进行高级操作。

2.点击建造启动构建过程。

在构建过程中,发生以下操作:

如下图所示,在新模型中生成一个名为Controller的文件块。不要关闭此模型。

在新模型生成之后,FIL向导打开了一个命令窗口,其中FPGA设计软件执行合成,拟合,地点和路由,时序分析和FPGA编程文件生成。

当FPGA设计软件流程完成时,命令行窗口中的一条消息允许您知道您可以关闭窗口。关闭窗口并继续下一步。

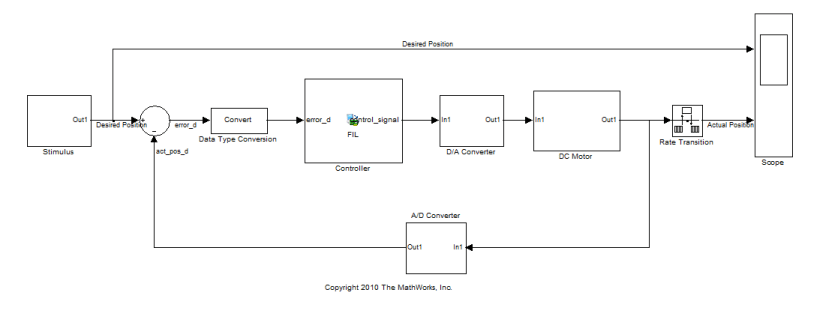

步骤10:建立模型

在fil_pid模型中,更换控制器子系统与新模型中生成的FIL块。修改后的fil_pid模型现在显示如下图所示:

步骤11:编程FPGA

1.开关FPGA开发板电源在。

2.双击fil_pid模型中的FIL块以打开块掩码。

3.在打开的块蒙版中,单击负载。

如果您的电路板正常通过JTAG电缆连接到主机,则显示一个消息窗口,以指示FPGA编程文件已成功加载。点击好的取消此对话框。

4.仅限以太网连接:您可以通过Ping测试正确测试FPGA板是否已正确连接到主机。启动命令行窗口并输入以下命令:

C:\ mytests> ping 192.168.0.2

如果在安装网卡时修改了单板的IP地址,请将“192.168.0.2”替换为单板的IP地址。如果千兆以太网连接已经正确设置,您应该看到来自FPGA开发板的ping应答。

第12步:审查FIL块的参数

1.在FIL块掩码中,单击信号属性选项卡。

2.验证数据类型HDL信号control_signal是Fixdt(1,32,28)。如果不是,改变它。

3.点击好的关闭块掩码。

步骤13执行命令FIL

1.开始仿真FIL_PID模型。

2.完成仿真时,在范围内查看电机所需和实际位置的波形。请注意,FIL模拟的结果应匹配模拟中的Simulink参考模型的结果金宝app准备资源的例子。