主要内容

AXI4-Interface读

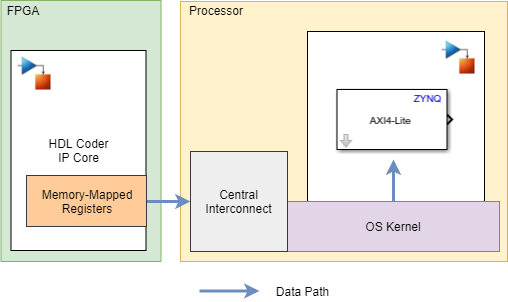

从IP核读取数据赛灵思公司Zynq平台

描述

该块从HDL Coder™生成的IP核上连续的内存映射寄存器组读取数据向量。的AXI4-Interface读块,利用处理系统的中央互连,提供简单的内存映射通信与FPGA上的IP核。此块最适合于低吞吐量通信,如检查状态、状态或控制寄存器。这个图显示了数据到达这个块之前的路径。

港口

输出

参数

另请参阅

AXI4-Interface写|AXI4-Stream IIO读|AXI4-Stream IIO写

主题

- Xilinx Zynq平台(高密度脂蛋白编码器)

- AXI4-Stream接口生成的模型设计(Xilinx Zyn金宝appq平台的HDL编码器支持包)

介绍了R2013a