このページの翻訳は最新ではありません。ここをクリックして,英語の最新版を参照してください。

高密度脂蛋白コード生成

FPGAまたはASICでDSP設計を実装するには,高密度脂蛋白编码器™または滤波器设计高密度脂蛋白编码器™を使用します。どちらの製品も,合成可能で移植可能な硬件描述语言(VHDL)®やVerilog®のコードを生成し,生成されたコードのシミュレーションやテスト,検証をすばやく行うための硬件描述语言(VHDL)やVerilogのテストベンチも生成します。

高密度脂蛋白编码器——金宝app仿真软件MATLABやの設計からコードを生成します。このサポートには,フィルター、数学演算,信号処理のほか,FFT HDL优化、传输线HDL优化、NCO HDL优化の各ブロックなど,リソースの使用とパフォーマンスについて最適化されたアルゴリズムが含まれています。高密度脂蛋白编码器を使用してHDLコードを生成する方法の基本的な例については,プログラミング可能なFPGA用冷杉フィルターを参照してください。

滤波器设计HDL编码器——MATLABのフィルター設計からコードを生成します。コードおよびテストベンチの生成機能には,[HDLを生成]ユーザーインターフェイスまたはコマンドラインオプションを使用してアクセスできます。これらの機能はフィルターデザイナーアプリにも統合されています。滤波器设计HDL编码器を使用して HDL コードを生成する方法の例については、高密度脂蛋白巴特沃斯滤波器滤波设计HDL编码器を参照してください。

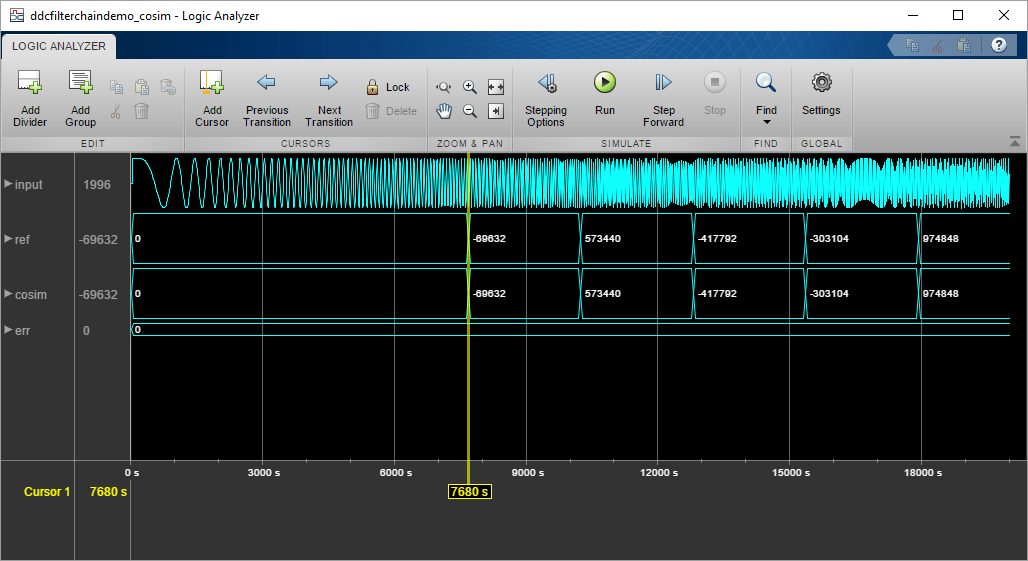

金宝appMATLAB仿真软件またはで設計をデバッグするには,ロジックアナライザーの波形ビューアーを使用します。

金宝app仿真软件可視化ツール

| ロジックアナライザー | 時間の経過に沿った遷移と状態の可視化,測定および解析 |

関数

generatehdl |

为量化的DSP滤波器生成HDL代码(需要滤波器设计HDL编码器) |

トピック

在Simulink库浏览器和文档中支持HDL代金宝app码生成的块的过滤器。金宝app

为过滤系统对象生成HDL代码滤波设计HDL编码器

了解从过滤系统对象生成HDL代码的细节。

选择HDL代码生成参数来控制滤波器架构中的速度和面积权衡。

选择资源共享和管道优化选项。

选择一个支持基于框架的输入的块来生成HD金宝appL代码。

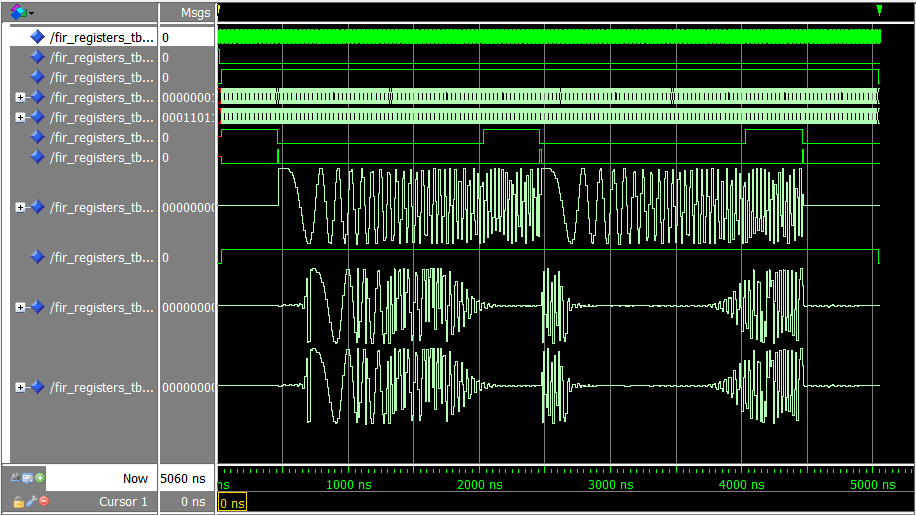

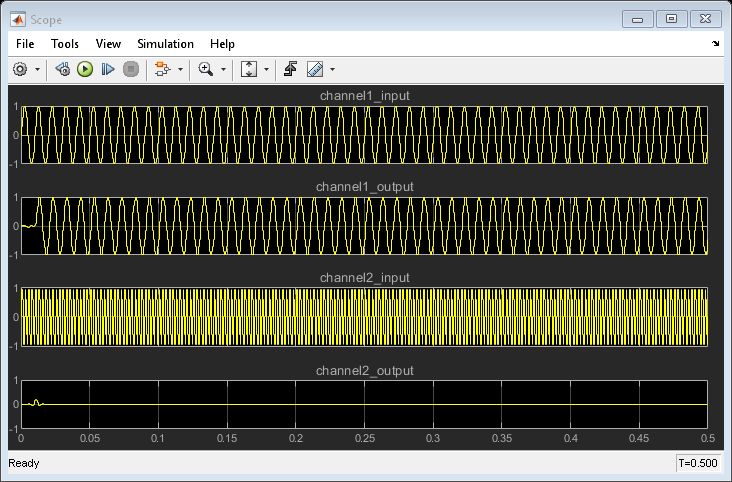

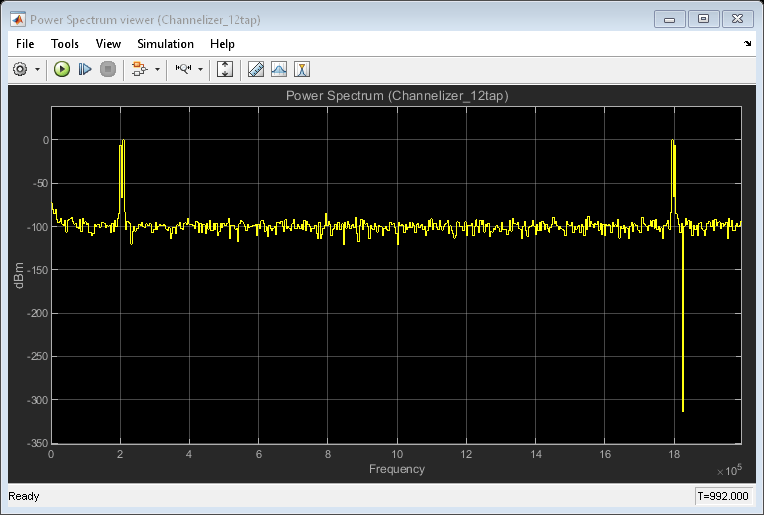

使用逻辑分析仪可视化可编程FIR滤波器的多个信号。关于这个示例中使用的模型的更多信息,以及如何配置模型生成HDL代码,看到プログラミング可能なFPGA用冷杉フィルター。