FPGA(现场可编程门阵列)는프로그래밍을통해기능을사용자지정할수있는디지털논리회로가포함된전자소자입니다。FPGA의논리는사용자의특정애플리케이션을수행하도록프로그래밍되어있으므로범용애플리케이션프로세서에서실행되는소프트웨어명령어보다더빠르고더적은전력으로이러한기능을실행할수있습니다。또한소자에프로세서가있는FPGA는시스템온칩또는SoC FPGA라고부릅니다。

FPGA를프로그래밍하는방법

MATLAB®또는仿金宝app真软件®에서알고리즘부터시작하는경우먼저인가및분석에서설계를분할하여하드웨어파티션의입력과출력을정의해야합니다。

하드웨어타겟팅을위한알고리즘에서테스트벤치요소분할。

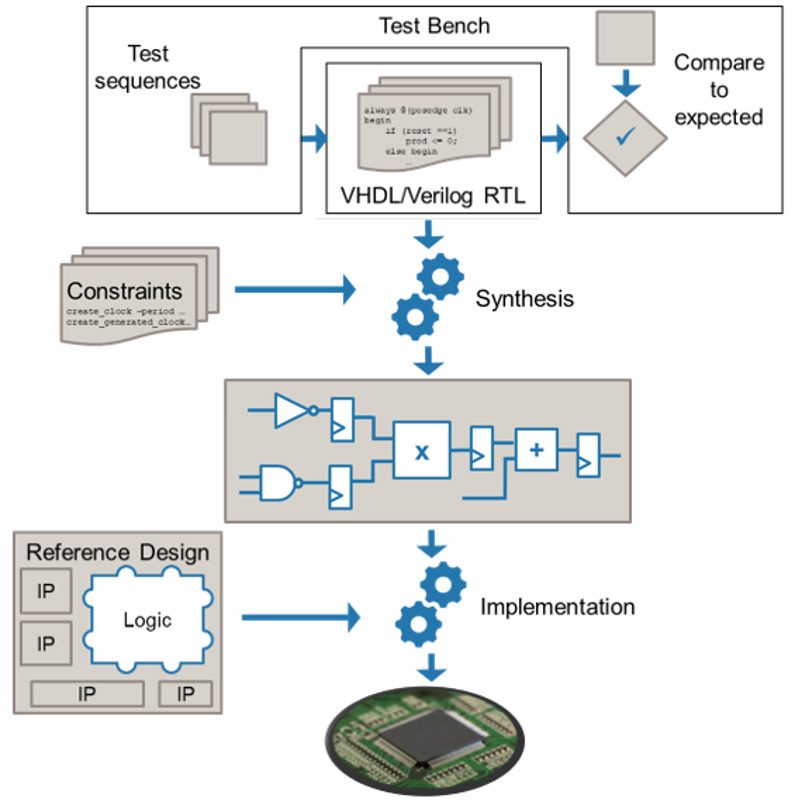

FPGA프로그래밍의주요단계:

- 하드웨어아키텍처설계。SoC FPGA의경우에는하드웨어-소프트웨어SoC아키텍처입니다。

- 설계。하드웨어논리자체를생성하는과정입니다。일반적으로硬件描述语言(VHDL)®또는Verilog®와같은하드웨어기술언어(HDL)를사용하여레지스터전달논리(RTL)를작성합니다。이단계의목표는효율성을위해고정소수점연산을이용하여지속적인데이터스트림에대해연산하면서알고리즘의기능을일치시키는것입니다。

- 검증。이단계에서는FPGA프로그래밍전에설계가의도한대로작동하는지확인합니다。확인과정은硬件描述语言(VHDL)또는Verilog테스트벤치와같이단순할수있습니다。상업용프로젝트에서는일반적으로UVM(统一验证方法)과같은방법론을이용합니다。

- 합성。이기술을통해서는RTL이디지털논리게이트로변환되고FPGA에서리소스의사용을최소화하면서레지스터——레지스터클럭주파수목표가충족되도록시도합니다。

- 통합。FPGA에는핀,클럭신호,아날로그——디지털변환기(ADC)와같은입출력처리및보드의오프칩메모리와다른기기인터페이스등의여러전용리소스가이미포함되어있습니다。SoC FPGA에도하드웨어와소프트웨어에서서로통신하는데이용할수있는전용레지스터가포함되어있습니다。사용자의설계를이”참조설계“에맞춰연결해야합니다。

- 구현。어떤논리로FPGA에서어떤물리적리소스를프로그래밍할지와이를연결(라우팅)하는방법을결정하는과정입니다。이를통해FPGA프로그래밍을위해소자로불러오는비트스트림이생성됩니다。

- 랩테스트및디버그。FPGA프로그래밍후실제입력또는테스트입력을사용하여실행할수있습니다。처음몇몇시도에서는대개작동하지않는이유와수정하는방법을알아보게될것입니다。이는대부분검증단계에서식별되지않은설계단계에서의문제로인해생긴것입니다。

알고리즘설계부터FPGA프로그래밍까지진행되는일반적인워크플로。

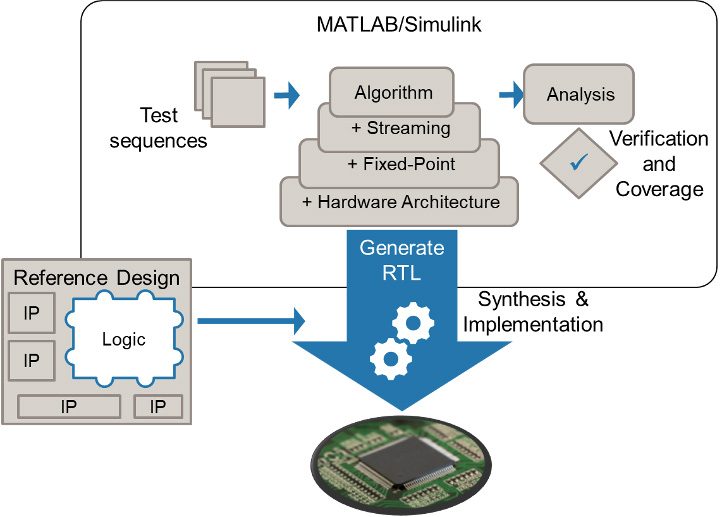

MATLAB및仿真金宝app软件를사용한FPGA프로그래밍

MATLAB및仿真金宝app软件에서알고리즘을모델링하면알고리즘과하드웨어아키텍처설계에집중할수있습니다。MATLAB및仿真金宝app软件를사용한FPGA프로그래밍의주요단계는다음과같습니다。

- 하드웨어아키텍처추가。일반적으로고정소수점데이터형을사용하여지속적인데이터스트림을처리하려면하드웨어아키텍처를추가하도록알고리즘을변경해야합니다。金宝app仿真软件는하드웨어아키텍처설계를위한시간기반시각적환경을제공합니다。이버전의설계를시뮬레이션한후골든알고리즘결과와비교하는것이이상적인방식입니다。

- 코드생성。하드웨어에대해준비된설계를얻으면高密度脂蛋白编码器™는做- 254및ISO 26262와같은기능안전워크플로에대한추적성과디버깅을위한모델까지의링크가포함된타겟독립적인Verilog또는硬件描述语言(VHDL) RTL을생성합니다。

- 통합。高密度脂蛋白编码器로FPGA프로그래밍을위해알고리즘을연결하려면참조설계가여전히필요합니다。다수의참조설계가하드웨어지원패키지를통해또는FPGA보드공급업체에서제공됩니다。

- 합성및구현。高密度脂蛋白编码器는RTL합성을위한스크립트와프로젝트를생성할수있으며,자동화된FPGA프로그래밍워크플로를제공하기위해赛灵思公司,英特尔및Microsemi의합성및구현툴과통합됩니다。

하드웨어세부사항으로알고리즘을미세조정한후합성가능한RTL을생성하여FPGA개발키트또는사용자지정보드를타겟팅합니다。

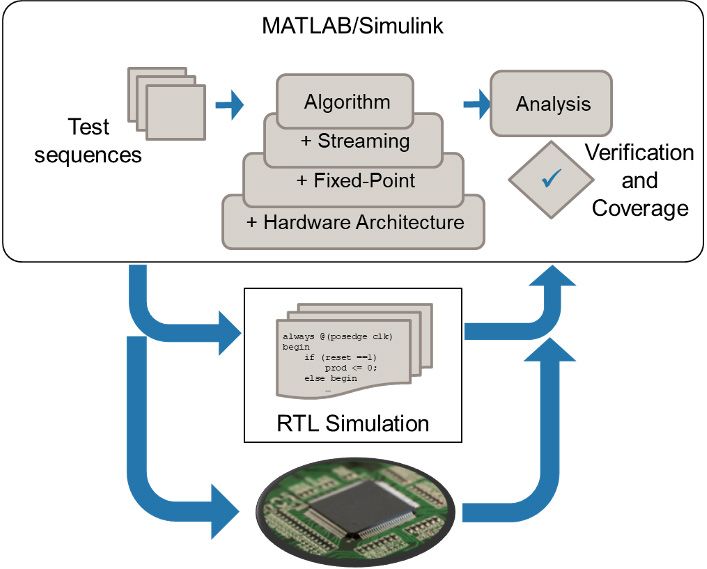

- 확인。RTL이알고리즘과동일하게기능하는지확인하는가장간단한방법은高密度脂蛋白验证器™를사용하여导师图形®,®또는节奏®Xcelium™에서실행되는RTL을MATLAB및仿真软件의金宝app설계및테스트벤치와함께시뮬레이션하는것입니다。FPGA에서의디버깅은가시성이훨씬더낮고더긴반복을필요로하므로FPGA프로그래밍전에가능한한많은시나리오와코너케이스를테스트하십시오。金宝app仿真软件测试™를사용하여테스트케이스를프로그래밍방식으로실행및관리할수있고,金宝app仿真软件覆盖™를사용하여설계를얼마나잘검증했는지측정할수있습니다。

- 랩테스트및디버그。高密度脂蛋白验证器를사용하여AXI마스터로사용되는MATLAB에서FPGA로데이터를분산하는논리를삽입하고,디버그를위해FPGA내부신호에서데이터를캡처하는논리를삽입할수있습니다。FPGA프로그래밍워크플로를위해사용하는지여부와는상관없이FPGA를직접디버그하기위해MATLAB및仿真软件를사용할수있습니다金宝app。

MATLAB및仿真金宝app软件를지원되는시뮬레이터또는FPGA보드에서실행되는구현된설계와함께시뮬레이션。