通过连接到MATLAB来提高RTL验证

杰克erickson,Mathworks

在生产中,FPGA,ASIC和SOC项目,RTL验证通常会消耗任何任务的最多时间和精力。尽管如此,虫子仍然以比所需的速度更高的速度将其变成硅。其中一个根本原因是算法设计之间的通信差距,通常在Matlab中开始®或者模金宝app拟®, and RTL design and verification. New algorithms are too complicated to rely on specification documents and hand-writing code.

此视频提出了对此通信差距的解决方案,以我们通常会看到我们的客户采用这些新技术的顺序提供:

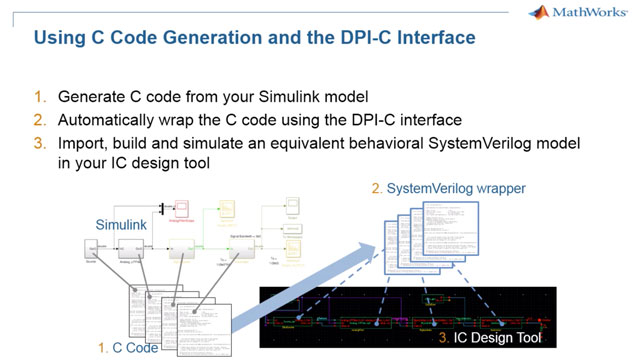

- SystemVerilog DPI组件生成:而不是依赖于算法工程师编写规范文档,即验证团队必须解释和编写测试用例和参考模型,您可以自动生成MATLAB或SIMULINK为您的SystemVerilog测试禁止的模型。金宝app如果规范更改,则会在算法中进行更改,测试它,并重新生成模型。

- Cosimulation:当您需要在RTL设计,测试台和系统或算法级设计之间调试问题时,可以将MATLAB或SIMULINK与RTL模拟器一起调试。金宝app这同时为算法和RTL提供了完全可见性,使算法工程师能够直接与验证和硬件设计工程师协作。

- 早期验证和验证:许多客户已开始以更多硬件详细信息更新其算法,例如流行为,定点数据类型和硬件架构。然后,他们建立可重用和自动化的测试环境,嵌入断言并测量覆盖范围。

这种分阶段采用的方法几乎立即产生了验证团队的益处,而且长期以来,长期鼓励系统/算法设计,硬件设计和硬件验证之间的协作,从而导致更强大和敏捷的开发过程。