采用基于模型的设计为FPGA,ASIC和SoC开发

杰克·埃里克森MathWorks

连接MATLAB®和Sim金宝appulink®数字硬件设计和验证已经帮助众多客户(下面的例子)缩短他们的日程安排,提高他们的验证效率,并在他们的FPGA,ASIC或SoC设计流程提供更高质量的结果。虽然这个工作流程似乎从现有的工作流程非常不同,你可以通过它逐步在实现眼前的利益。

了解如何:

- 结合使用MATLAB和Simulink的优点,通过更详细的实现细节来改进算金宝app法

- 构建可重用的测试工作台基础设施

- 生成SystemVerilog验证组件,以加速RTL验证环境的开发

- 算法和数字硬件工程师之间进行合作,早期收敛高效的硬件体系结构

- 自动化并管理定点转换过程,甚至利用本地浮点实现,因为它更高效

- 生成无错误的可合成RTL,以针对任何FPGA、ASIC或SoC设备

本文概述了一些经过验证的入门方法,以及从这些方法开始的典型采用路径。

例子:

您可能听过我们的一个或多个客户谈论将MATLAB和Simulink连接到他们的FPGA、ASIC或SoC设计工作流的好处。金宝app你可能会看着它,觉得它离你现在的位置还很远。但是所有这些客户都开始采用一两个功能来帮助解决他们最紧迫的挑战之一,并逐步构建完整的工作流。

我们将首先展示构建一个更具协作性和互联性的芯片设计环境的高级好处,但是主要的重点是如何开始,以及我们看到我们的客户采取的一些更常见的初步步骤,以及他们从哪里开始。然后我们会总结一些来自我们客户的真实体验。

如果我们看看今天的芯片设计项目,使用Mentor Graphics和Wilson Research Group提供的优秀调查数据,67%的项目落后于计划。

而综观上面的瓶颈,脱颖而出的一个验证,平均为50的项目时间% - 但最常见的,对于ASIC是60-70%,而FPGA是约50-60%。

即使所有这些努力,ASIC项目的75%仍需要重新流片,它在数百万美元,但更糟糕的直接成本,可以通过几个月会导致您的日程单。

同样的调查显示,84%的FPGA项目仍然看到非平凡的bug进入生产。很多人认为这没什么大不了的,因为fpga毕竟是“现场可编程”的,但如果是在太空中的卫星上,就很难重新编程了。如果产品中含有这种物质,比如工厂的检测设备,就可能导致生产线关闭,或者你可能不得不召回产品。最后,你真的不希望硬件bug跑到飞机和汽车上。

这一切的根源在于芯片设计是一个复杂的过程,需要关键的贡献和大量的专业技能。但是他们每个人都有自己的工具和环境,并且有太多的项目依赖于手动通信技术,比如手写的规范文档或会议,以获得成功。当有不完整的信息时,就会做出假设或局部决策,往往会导致一些问题,而这些问题只有在项目结束时系统才会出现,而修复这些问题的成本很高。敏捷,这使得它几乎不可能是在适应变化的需求,就像杰米在快板微系统所指出的那样,汽车传感器ASICs-definitely多学科设计混合信号产品,严格的质量要求,但他们也需要为每个汽车制造商敏捷开发定制的功能。

如果您熟悉基于模型的设计,这可能看起来很熟悉。如果不是,请不要担心。

通常的今天,这部分初期仅是在系统和算法设计人员,谁是集中在“我到底在做什么?”在设计方面,而“我在做正确的事情?”或验证。然后,他们手头宽裕这些规范的各种实施工程师独立工作,以“让”,并确认他们已经“做是正确的。”如果一个或多个基团使这些地方的决策无论出于何种原因之一,它会导致未发现,直到为时已晚的问题。

缺少的关键是将实现知识引入到早期部分中,在他们开始之前尽早弄清楚“我们将如何实现它”和“它将如何工作”,当然,在实现的过程中不断地重新集成。正是这种联系让一切运转起来,这就是我们在这里所关注的。

因此,让我们用一般的方法我们的客户通常需要启动。

从根本上说,我们希望得到我们的算法到硬件。首先,我们可能需要他们适应工作在连续的数据流,并尽可能地在硬件资源使用方面是有效的,同时还能满足功能性和吞吐量要求,而且通常包括量化数据为定点。处理客户我们的许多信号处理,无线,和视频/图像的主要处于MATLAB,这当然是极大的探索数学,操纵数据集,和编程控制。但是,如果你的目标硬件,可以并行这就要求并行路径的定时进行管理的过程,Simulink则是大了点。金宝app这也为架构的可视化,以及如何定点数据类型通过操作传播不错。这种做法的好处是这两种环境很好地协同工作,以便我们改进这些算法,我们可以用最好的两个,顺利过渡。

通常第一步是分区。很多时候,算法和它们的测试会在同一个MATLAB脚本中交织在一起。所以我们需要区分哪些是针对硬件的。这也是帮助构建更健壮和自动化测试环境的良好实践。在这个例子中,我们使用了一个脉冲检测算法,它非常简单——它将一个信号与一个匹配的滤波器相关联,在匹配的地方产生一个峰值。这就是硬件设计。剩下的部分将是测试阶段——输入刺激,我们不会详细讨论,以及分析,目前只是一些可视化和fprintf语句。

关注算法——它获取一个完整的信号,通过过滤器运行它,然后max函数找到全局峰值。但在硬件方面,我们有源源不断的数据。所以我们需要调整算法来处理这个问题。

我们也将在Simulink中使用一些MATL金宝appAB来构建它。我们仍然可以使用相同的测试环境,从“from Workspace”块中获取输入,然后通过“To Workspace”块将其发送回去。对于过滤器,我们有一个流杉木块-这很简单。然后我们需要求出大小的平方,我们可以把它构造成实函数和虚函数的平方。现在,为了找到最大值,我们只需要存储最近11个样本的一个滚动缓冲区。

这是很容易在MATLAB程序,所以我们可以使用一个MATLAB函数块,这将通过检查找到这些11个样品的峰值如果中间样品比其它的大,并且还高于最小阈值被识别为一个“峰“。因为这是不断流,它输出一个脉冲,以表示该中央样品是所识别的峰。

现在,从验证的角度来看,我们已经划分从激励和分析设计。这将使我们能够在任何精致设计的版本的交换和比较仍对黄金参考算法。验证工程师们通常把这种功能的“记分牌”。同时注意我们添加了一些自我检查能力;这将使我们能够运行在批量模拟和容易检查结果。

在这一点上,你实际上可以生成组件,以启动该RTL验证过程。记住怎样的时间表有多少是通过验证消耗?通过自动生成测试和极好的参考模型帮助这个过程中一起帮助他们开始得更早,不必开发和调试他们自己的版本。这是C代码包裹着的SystemVerilog,因此它在任何的SystemVerilog模拟器本地运行。因为它是自动生成的,你可以把它作为规范的可执行版本,当设计变更,您只需重新生成。这是开始使用产生一个非常简单的方法模型,它的工作原理可以从MATLAB或Simulink中生成的任何地方的C代码。金宝app

如果RTL仿真确定了不匹配,可以通过联合仿真MATLAB或与RTL仿真连接的Simulink进行调试。金宝app因为您有算法和RTL的实时模拟器,所以您可以看到两边的调试,并且它们是同步运行的。考虑到这些,您可能不会以这种方式运行回归,但是当您需要与实际的黄金参考算法进行比较时,它确实有助于调试问题。

类似于适应你的算法流的行为,细化的一个新的水平是增加硬件架构。有很多的建筑级的决定,这将影响硬件性能和资源的使用,这确实需要的硬件设计人员的专业知识。显示在这里,找到了复杂的滤波器输出的大小一些例子,你用勾股定理,但平方根运算是在硬件资源和时延非常昂贵。知道我们只需要找到最大的一组值的,我们就可以跳过这一步 - 所以这是与算法的知识一起工作的硬件实现的知识,可以更有效地让你很好的结果。

一个更简单的例子是选择FFT实现选项,在FFT块上,您可以设置基数、如何实现复杂的乘法以及添加管道阶段。

而通常针对硬件要求定点量化,以减少资源的使用。但是这会降低精度,所以有一个效率与准确度的权衡,可以成为一个费时的背和反复的过程。但是,我们有几个办法是帮助这个过程自动化和驱动它走向趋同,所以这是另一种能力,我们看到客户采用作为第一步。

第一种方法是手动转换输入,并让Simulink在逻辑中适当地传播。金宝app在本例中,我们将乘法的输入设置为18位,以确保它们映射到FPGA上的DSP片。输出可以通过默认传播增长,但是我们将下一阶段的sum的输出减少到18位。这就是Simulink的可视金宝app化真正派上用场的地方。这种方法是一个很好的平衡起点,您可以通过一些小的调整来收敛。

如果需要对数据类型进行更细粒度的控制,那么定点设计器可以帮助实现自动化和管理。的步骤将指导您完成模拟代表性样本的测试,收集数据范围,那么它将提出定点类型的数据范围,然后您可以使用原有或调整,模拟使用这些类型为双精度比较,看看结果是在公差内。它还将查看这里图形化显示的溢出/下溢条件。

而第三个选项是生成使用HDL编码器原生浮点运算的硬件。这是加快更敏感操作的量化是有用的。就拿这里这个简单的例子,如果有人显然花了很多的时间来构建一个查找表来计算与精度30位的32位输入正弦余弦操作。节省了大量的时间,你可以在这里使用单精度数据类型,并生成硬件执行本地浮点正弦余弦计算。是的,查找表将在硬件资源方面更有效,但如果你只是希望获得到的硬件和你有足够的资源,这种方法需要大量的时间更少。

在这种情况下,HDL编码器可以共享正弦和余弦硬件资源。它支持金宝app广泛的操作符和优化,因此您可以在硬件中实现这些操作符而不牺牲准确性。这对于高动态范围的计算特别有用。您可以将其用于整个设计,或者仅用于如图所示的孤立区域。生成与目标无关的RTL。

Demcon将这种能力用于外科器械的精确马达控制算法。您可以在这里看到他们的结果,其中it确实使用了更多的硬件资源,但是开发工作量却减少了五倍。要了解更多细节,可以在MathWorks网站上查看他们的用户故事。

是的,一旦你到那里你有硬件架构的流算法和你的执行工作,这是很容易产生用HDL编码器综合的VHDL或Verilog的NUMERICS点。有数百个硬件就绪块,你可以使用嵌入式MATLAB代码或Stateflow图,其中它的效率更高,例如,对于复杂的控制逻辑。你有很多的用于应用硬件专业知识的探索和控制的优化,或者只是用它来快速上手的默认选项。我们在内置设置,包括映射到不同的AXI总线接口的目标有很多,我们必须创建自定义目标的能力。大约在高位设计的探索,进行更改,而不必大约进行手动编码错误的担心生成代码的非常好的一部分。

这些AXI总线接口通常是硬件子系统与其他芯片级子系统和处理器上的软件通信的方式,使用这些协议通信的延迟通常需要建模。类似地,使用外部内存需要通过具有延迟的内存控制器进行读写,延迟可能会影响硬件体系结构和算法的功能。SoC块集提供了这些效果的模拟模型,因此您可以模拟真实的上下文,并在进入硬件之前甚至在进行硬件和软件之间的分区之前就得到正确的结果。

最后,让我们重新审视我们的客户的例子。

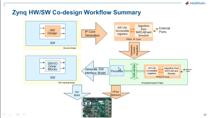

这些是快板看到的结果;他们现在在Simulink中一起设计和模拟他们的模拟和数字功能,早期调试问题,并利用实现细节对其进行改进,不断地集成改进的模型以进行验证。金宝app这允许他们仍然并行地进行开发,同时不断地一起验证所有东西,以消除后期的意外。一旦他们得到了一个可实现的模型,他们就会生成一个可集成的RTL来进行实现,并且他们还会为他们的验证环境生成DPI组件。Jaimie在录制的MATLAB Expo视频中提供了更多的细节。我鼓励你们去看看。

To get started with Model-Based Design for implementing hardware, it’s best to take an incremental approach, partitioning and refining your algorithms with implementation detail by collaborating between algorithm and hardware design, and starting with verification models or maybe fixed-point conversion to get some early return on a small investment. This will not only eliminate those communication issues but by getting these folks working together, you’ll get a better overall design. As you get more comfortable and move toward designs you can generate synthesizable RTL for, you will have the agility to easily re-generate for changing requirements.

如果你有兴趣了解更多关于如何最好地上手,比如与验证与定点转换,或向炼硬件实现一个MATLAB算法,就可以得到更详细的这些技术从这些资源,或者您也可以直接如下所示与销售人员联系我们交谈。

你也可以从以下列表中选择一个网站:

如何获得最佳的网站性能

选择最佳的网站性能的中国网站(在中国或英文)。其他MathWorks的国家网站都没有从您的位置访问进行了优化。