速度与区域权衡

速度或区域优化概述

在实现滤波器设计时,编码器提供了扩展速度与区域权衡控制的选项。要达到预期的折衷,您可以指定完全平行架构生成的HDL过滤器代码,或选择其中之一序列号架构。这些体系结构在并行和串行架构.

下表总结了可用于并行和串行体系结构选择的过滤器类型。

| 体系结构 | 可用于过滤器类型...... |

|---|---|

完全平行(默认) |

生成HDL代码时支持的筛选器类型金宝app |

全系列 |

|

部分系列 |

|

级联序列 |

|

该编码器通过传递给金宝app生成hdl函数,如通过generatehdl属性指定速度和区域的权衡.

或者,您可以使用体系结构弹出式菜单在Generate HDL对话框中选择并行和串行架构选项,如在Generate HDL对话框中选择架构.

请注意

该编码器还支持分布式算术(DA金宝app),用于实现过滤器的另一个高效架构。看到FIR滤波器的分布式算法.

并行和串行架构

完全并行体系结构

此选项是默认选择。A完全并行体系结构为每个过滤器轻拍使用专用乘法器和加法器;抽头并行执行。这种类型的架构是速度最佳。但是,它需要更多的乘数和加法器,而不是串行架构,因此消耗更多芯片区域。

串行架构

串行架构及时重用硬件资源,节省芯片面积。编码器提供一系列串行架构选项。这些架构有一个时钟周期的延迟(参见串行架构中的延迟).

您可以从这些串行架构选项中选择:

全系列:全串行架构通过顺序重用乘法器和加法器资源来节省区域。例如,一个四次点击的过滤器设计将使用一个乘法器和加法器,为每次点击执行一次乘法/累积操作。该设计的乘/累积部分以输入/输出采样率的四倍运行。这种类型的架构以速度损失和更高的功耗为代价节省了面积。

在全串行结构中,系统时钟的运行速率远高于滤波器的采样速率。因此,对于给定的滤波器设计,全串行结构可达到的最大速度小于并行结构的最大速度。

部分系列部分串行架构涵盖了完全并行和完全串行架构之间的速度和区域权衡的全部范围。

在部分串行架构中,过滤器插孔被分组到串行分区中。每个分区内的点击是串行执行的,但分区是并行执行的。分区的输出在最终输出处相加。

当选择部分串行架构作为筛选器时,可以通过以下方式定义串行分区:

直接将串行分区定义为整数向量。向量的每个元素指定相应分区的长度。

指定所需的硬件折叠系数

ff,一个大于1.给定折叠因子,编码器计算串行分区和乘数。指定所需的乘数数

nmults,一个大于1.给定乘数,编码器计算序列划分和折叠因子。

“生成HDL”对话框允许您根据这三个参数指定部分串行架构。然后,您可以查看一个参数的更改如何与其他两个参数交互。编码器还提供

hdlfilterserialinfo,一个信息函数,可帮助您为筛选器定义最佳串行分区。级联序列级联-串行体系结构非常类似于部分串行体系结构。就像在部分串行架构中一样,过滤器点击被分成几个并行执行的串行分区。但是,每个分区的累积输出级联到前一个分区的累加器。分区的输出因此在第一个分区的累加器处计算。这种技术被称为累加器重复使用. 您不需要最终的加法器,这样可以节省面积。

级联串行结构需要额外的系统时钟周期来完成对输出的最终求和。因此,相对于非编码部分串行架构中使用的时钟,系统时钟的频率必须稍微增加。

要生成级联-串行体系结构,需要指定启用累加器重用的部分串行体系结构。如果不指定串行分区,编码器将自动选择最佳分区。

串行架构中的延迟

滤波器的串行化将设计的总延迟增加一个时钟周期。串行体系结构使用累加器(带寄存器的加法器)来添加顺序乘积。使用附加的最终寄存器来存储每个串行分区的求和结果。该操作需要额外的时钟周期。下载188bet金宝搏

将输入数据保持在有效状态

串行架构实现内部时钟速率高于输入速率。在这样的过滤器实现中,有N周期(N > = 2)的基时钟。您可以指定测试台在有效状态下保存输入数据值的时钟周期。

当你选择在样本之间保留输入数据(默认情况下),测试台将输入数据值保持在有效状态,以便

N时钟周期。你什么时候离开在样本之间保留输入数据,测试台仅在一个时钟周期内以有效状态保存输入数据值。为下一个

n - 1周期时,测试台将数据驱动到未知状态(表示为“X”),直到输入下一个样本。将输入数据强制为未知状态将验证生成的筛选器代码仅在第一个循环中注册输入数据。

图中显示了试验台“生成HDL”对话框中的在样本之间保留输入数据设置为其默认设置。

使用等价物样本之间的HoldInputData属性时,调用生成hdl函数。

指定速度与区域权衡通过生成hdl属性

默认情况下,生成hdl使用完全并行的体系结构生成过滤器代码。如果希望生成具有完全并行体系结构的过滤器代码,则不必显式指定此体系结构。

控件的两个属性指定串行架构选项生成hdl功能:

串行分区:此属性指定筛选器的串行分区。ReuseAccum:此属性启用或禁用累加器重用。

该表总结了如何设置这些属性以生成所需的体系结构。

| 产生这 架构…… |

设置SerialPartition…… | 设置ReuseAccum…… |

|---|---|---|

| 完全平行 | 省略这个属性 | 省略这个属性 |

| 全系列 | N,在那里N是过滤器的长度吗 |

未指定,或“关” |

| 部分系列 |

您还可以根据所需的硬件折叠因子或最佳乘法器数量来指定串行体系结构。看见 |

“关” |

| 具有显式指定分区的级联串行 | [p1 p2 p3…pN]:具有N元素,N是串行分区的个数。向量的每个元素指定了对应分区的长度。向量元素的和必须等于过滤器的长度。vector元素的值必须按降序显示,但最后两个元素必须相等。例如,对于长度为9的过滤器,分区如(5 - 4)或者[4 3 2]将是合法的,但分区[3 3 3]或者[3 2 4]在代码生成时引发错误。 |

“上” |

| 具有自动优化分区的级联串行 | 省略这个属性 | “上” |

您可以使用helper函数hdlfilterserialinfo为您的过滤器探索可能的分区。

有关示例,请参见为FIR滤波器生成串行分区.

IIR SOS过滤器的串行架构

为IIR SOS过滤器结构指定部分或完全串行架构(df1sos或者dsp。BiquadFilter),指定以下任一参数:

“折叠因子”,ff:指定所需的硬件折叠系数ff,一个大于1的整数。给定折叠因子,编码器计算乘法器的数量。“nummulti钳子”,n结果:指定需要的乘数nmults,大于1.给定乘法器的数量,编码器计算折叠因子。

要获得关于折叠因子选项和过滤器相应乘数的信息,调用hdlfilterserialinfo函数。

有关示例,请参见为IIR滤波器生成串行架构.

在Generate HDL对话框中选择架构

的体系结构弹出菜单,在“生成HDL”对话框中,允许您选择并行和串行体系结构。以下主题描述了您必须为每个的UI选项体系结构选择。

指定完全平行的架构

默认值体系结构设置是完全平行,如图所示。

指定完全串行架构

当你选择全系列,体系结构选项时,Generate HDL对话框显示有关折叠因子、乘数和串行分区的附加信息。因为这些参数依赖于过滤器的长度,所以它们以只读格式显示,如下图所示。

生成HDL对话框还显示查看详细信息链接。当您单击此链接时,编码器将在单独的窗口中显示HTML报告。该报告显示了当前过滤器的折叠因子、乘数和串行分区设置的详尽表。您可以使用该表来帮助您为您的设计选择最佳设置。

为部分串行体系结构指定分区

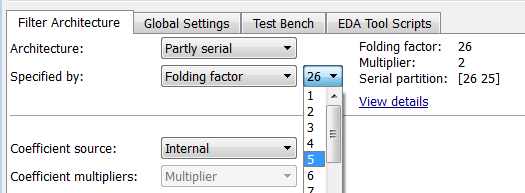

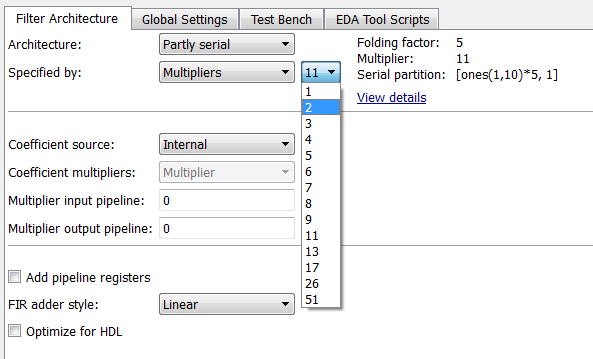

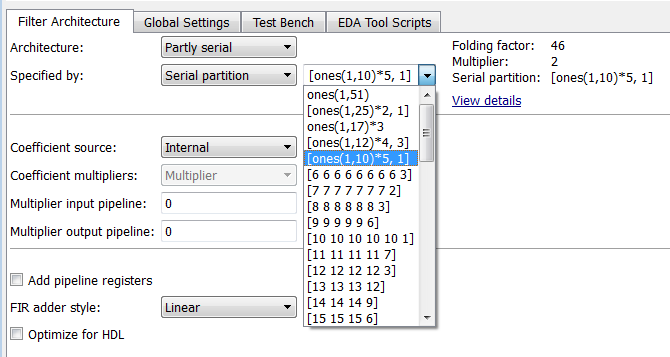

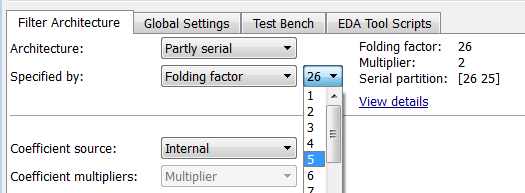

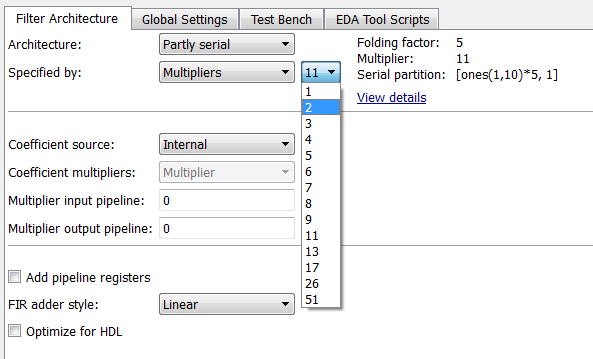

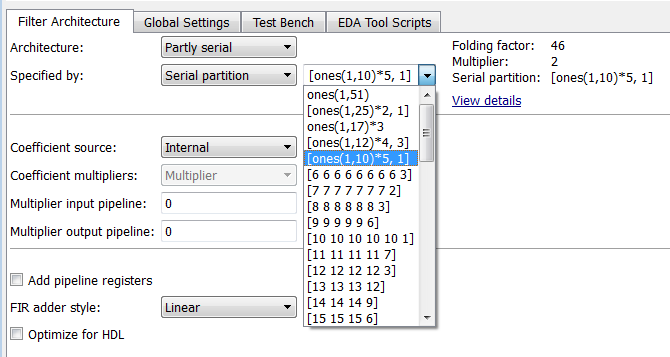

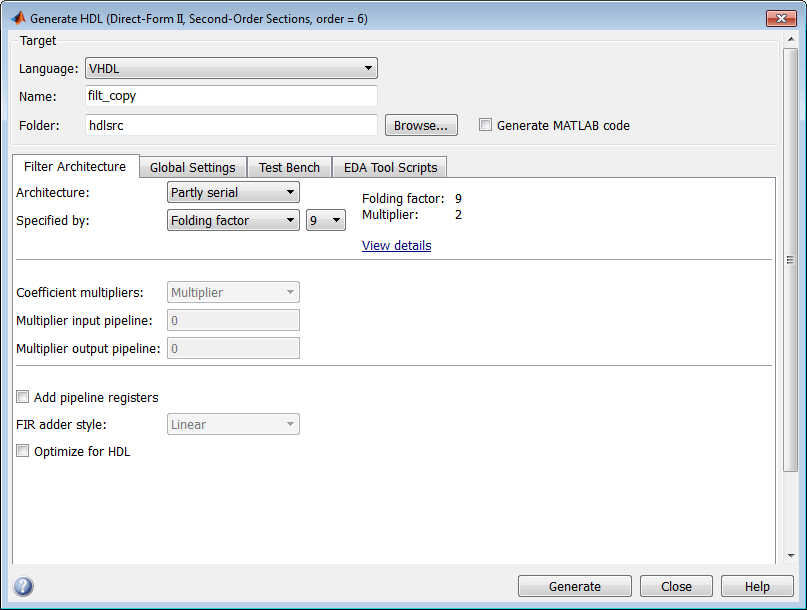

当你选择部分系列体系结构选项时,GenerateHDL对话框将显示与串行分区相关的附加信息和数据输入字段(请参见下图)

生成HDL对话框还显示查看详细信息链接。当您单击此链接时,编码器将在单独的窗口中显示HTML报告。该报告显示了当前过滤器的折叠因子、乘数和串行分区设置的详尽表。您可以使用该表来帮助您为您的设计选择最佳设置。

的指定的下拉菜单允许您决定如何定义部分串行架构。选择下列选项之一:

折叠的因素:右侧的下拉菜单折叠的因素包含筛选器的折叠因子的详尽列表。选择值时,当前折叠因子、乘数和串行分区设置的显示将更新。

乘数:右侧的下拉菜单乘数包含过滤器的乘数数量的穷举选项列表。选择值时,当前折叠因子,乘数和串行分区设置更新的显示。

串行分区:右侧的下拉菜单串行分区包含筛选器的串行分区选项的详尽列表。选择值时,当前折叠因子、乘数和串行分区设置的显示将更新。

指定级联串行架构

当你选择级联序列体系结构选项时,生成HDL对话框显示串行分区字段,如下图所示。

的指定的菜单允许您根据不同的标准定义串行分区的数量和大小,如通过generatehdl属性指定速度和区域的权衡.

为IIR SOS过滤器指定串行架构

要在UI中为IIR SOS过滤器结构指定部分或完全串行架构,可以设置以下选项:

体系结构:选择

完全平行(默认),全系列,或部分系列.如果您选择部分系列,UI显示指定的下拉菜单。指定的:选择以下选项之一:

折叠的因素:指定所需的五金件折叠系数,ff,一个大于1的整数。给定折叠因子,编码器计算乘法器的数量。乘数:指定所需的乘数,nmults,大于1.给定乘法器的数量,编码器计算折叠因子。

例如:直接形式I SOS过滤器。下面的示例创建一个直接表格I SOS (df1sos)过滤设计并打开UI。代码示例下面的图显示了为部分串行架构配置的编码器选项折叠的因素18。

Fs = 48 e3%采样频率Fc = 10.8 e3%截止频率N = 5%过滤顺序f_lp = fdesign.lowpass('n,f3db',N, f, f) filt = design(f_lp,“黄油”,“FilterStructure”,'df1sos',“SystemObject”,true)fdhdltool(filt,numerictype(1,16,15)))

例如:直接形式II SOS过滤器。以下示例创建一个直接表格II SOS (DF2SOS.)使用过滤器生成器进行过滤器设计。

滤波器是低通的DF2SOS.过滤器的过滤顺序为6。过滤算法设置为定点.

在代码生成选项卡,生成HDL.按钮激活Filter Design HDL Coder™UI。下面的图显示了为这个过滤器配置的HDL编码器选项,使用了部分串行架构折叠的因素第9页。

指定分布式算法体系结构

的体系结构弹出菜单还包括分布式算法(DA)选择。看到FIR滤波器的分布式算法)以获取有关此架构的信息。

架构选项和其他HDL选项之间的交互

选择特定的体系结构菜单选项可以改变或禁用其他选项。

当

全系列选项已选择,将以下选项设置为默认值并禁用:乘数系数

添加流水线寄存器

FIR加法器样式

当

部分系列选项被选中时:的乘数系数选项设置为其默认值并被禁用。

如果过滤器是multirate,则时钟输入选项设置为

单身的和残疾人。

当

级联序列选项已选择,将以下选项设置为默认值并禁用:乘数系数

添加流水线寄存器

FIR加法器样式