主要内容

优化

资源使用,时钟速度,芯片区域,延迟

过滤器设计HDL Coder™提供过滤器优化选项,以提高生成的HDL代码的硬件实现的速度或区域。默认过滤器实现是包含乘法器的完全并行架构。使用这些优化来修改HDL中过滤器的实现:

管道登记 - 见用流水线提高过滤器性能。

部分或完全串行架构 - 见速度与区域权衡。

分布式算术(DA)架构 - 见FIR滤波器的分布式算术那

规范签名的数字(CSD)或因子CSD技术 - 见CSD系数乘法器优化。

职能

hdlfilterdainfo. |

过滤架构的分布式算术信息 |

hdlfilterserialinfo. |

过滤体系结构的串行分区信息 |

特性

| HDL优化属性 | 优化生成的HDL代码的速度或区域 |

话题

为过滤器指定并行,串行,部分串行和级联体系结构。了解这些选择产生的优化权衡。

使用分布式算法实现FIR滤波器的有效乘法电路。

描述级联过滤器的架构选项:串行,分布式算术和并行。

使用规范签名的数字(CSD)或因子CSD技术来优化乘法器操作。

通过生成管道寄存器来优化生成的过滤器代码以实现速度。

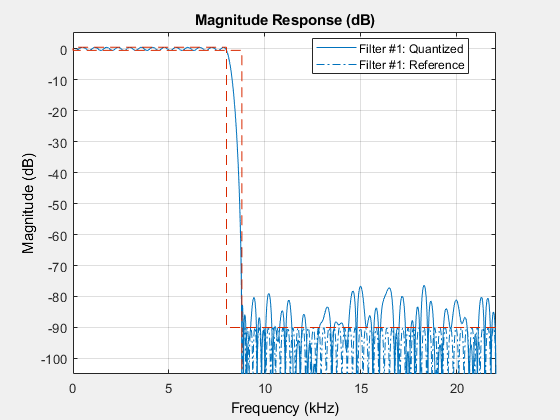

全局优化以及如何处理优化的HDL代码与原始设计之间的数字差异。

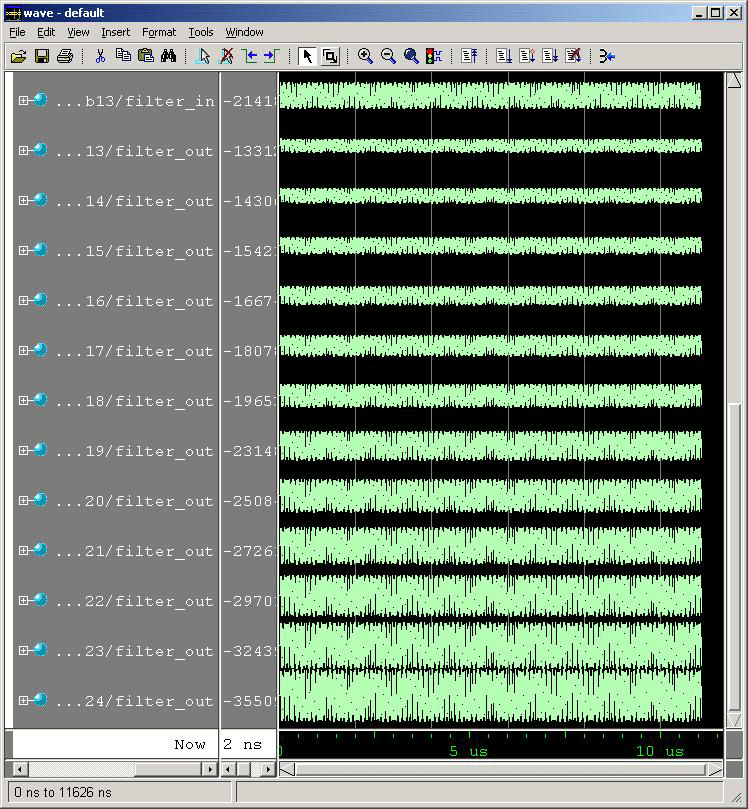

设计优化的FIR筛选器,为过滤器生成Verilog代码,并使用生成的测试台验证Verilog代码。