生成HDL代码使用模拟风景HDL工作流顾问

如果您拥有HDL Coder™的许可证,您可以使用Simscape HDL Workflow Advisor从Simscape™模型生成HDL代码,以便部署到FPGA平台上。Simscape HDL Workflow Advisor首先帮助您将Simscape模型转换为Simulink金宝app®实现。然后使用HDL编码器将Simulink模型转换为HDL代码。将Sim金宝appscape模型转换为HDL代码可以:

通过使用Simscape模型的优化实现加速物理系统的模拟

利用FPGA的可重构性和并行性功能进行快速原型设计

使用硬件在环(HIL)仿真实时模拟HDL实现

模拟风景HDL工作流顾问步骤

使用Simscape HDL workflow Advisor将Simscape模型转换为HDL代码的一般工作流包括以下步骤。

为您的Simscape模型生成基线结果。

方法确保模型只包含线性或可切换的线性块

simscape.findNonLinearBlocks函数。这个函数检测Simscape模型中的非线性块。该函数根据网络所包含的块返回网络的数量和类型,即线性、切换线性或非线性。该函数还返回产生非线性方程的任何块的名称。更新或替换产生非线性方程的任何块。确保模型的模拟结果(现在不包含产生非线性方程的块)与基线结果相匹配。

为实时仿真和HDL代码生成配置Simscape网络:

添加允许您在模拟时间方面监控HDL工作流的进度的块。

显示样本时间信息。

为固定步长、固定成本模拟配置Simscape网络。

确保离散模型的模拟结果与基线结果相匹配。

使用运行Simscape HDL Workflow Advisor任务

sschdladvisor作用这个sschdladvisor功能:检查HDL代码生成的兼容性,确保模型是线性切换的,并为实时仿真配置。

提取Simscape网络的状态空间系数。

生成Simscape网络的HDL代码生成兼容实现。

确保来自HDL代码生成兼容实现的模拟结果与基线结果相匹配。

生成HDL代码:

通过运行金宝app

hdlsetup作用这个hdlsetup函数配置用于HDL代码生成兼容性的固定步长求解器,并指定模拟的启动和停止时间。保存模型参数和验证模型生成设置。

使用

makehdl函数。

限制

Simscape HDL Workflow Advisor不适用于包含以下内容的Simscape网络:

事件。

模式的图表。

延迟。

启用运行时参数。

周期性的来源。

由网络连通性引起的非线性。如果你的模型确实包含这种非线性,那么

sschdladvisor函数可以运行所有任务直到完成,但生成零值输出。

生成HDL代码模拟风景模型使用模拟风景HDL工作流顾问

这个示例展示了如何使用Simscape HDL Workflow Advisor将Simscape模型转换为HDL代码。要了解如何配置Simscape网络和Simulink模型以进行实时仿真和HDL代码生成,请参阅金宝app模型制备. 要打开已准备好使用Simscape HDL Workflow Advisor的模型版本,请参阅使用Simscape HDL工作流顾问生成HDL代码.

模型制备

准备Simscape模型,以便将其转换为用于FPGA部署的HDL代码:

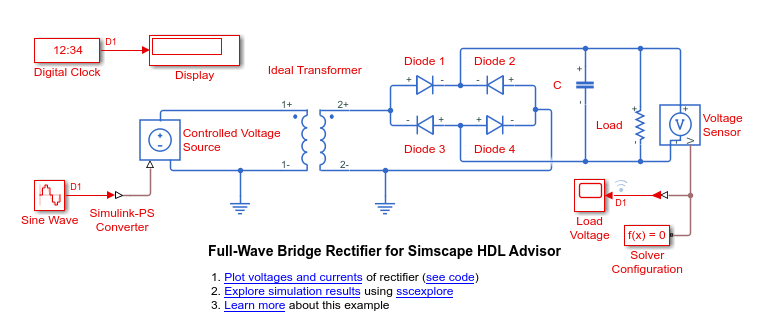

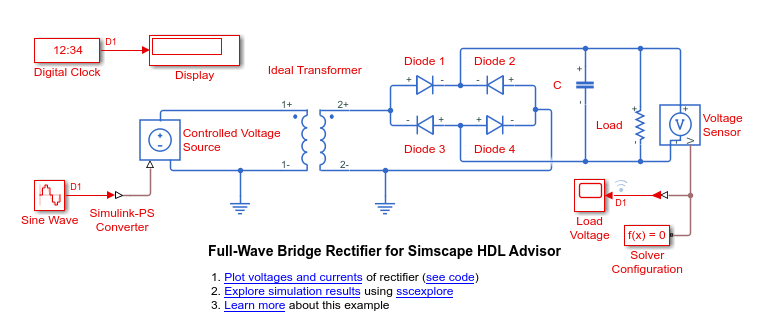

打开模型并显示隐藏的块名称。在MATLAB®在命令提示下,输入

baselineModel =“ssc_bridge_rectifier”; 加载系统(基线模型)设置参数(基线模型,“HideAutomaticNames”,“关”)开放式系统(基线模型)

为了将基线模拟结果与稍后的模型修改版本的结果进行比较,请去掉数据点限制负载电压scope块,并允许模拟数据检查器对输入数据到scope的信号进行数据记录。

在作用域的配置参数中日志记录参数,清除该选项以限制数据点。

的连接线单击鼠标右键负载电压范围块并选择

日志选择信号.

伐木徽章

在模型中标记信号。

在模型中标记信号。在模拟数据检查器中模拟模型并查看结果。

%%模拟基线模型sim (baselineModel)%%获取模拟数据检查器运行idrunIDs=Si金宝appmulink.sdi.getAllRunIDs;runID=runIDs(结束);run=Simulink.sdi.getRun(runID);signal1=run.getSignalByIndex(1);%run.signalCountsignal1.checked=true;Sim金宝appulink.sdi.view

根据需要,按键盘上的空格键以适应要查看的模拟数据检查器图。

对全波桥式整流负载电压的基线仿真结果与预期一致。

Simscape HDL Workflow Advisor不能将非线性网络转换为HDL代码。在运行advisor之前,确定并替换导致网络非线性的块。要识别积木,请使用

simcape.findnonnearblocks函数。simscape.FindOnlinearBlock(基线模型)

在以下模块中找到包含非线性方程的网络:“ssc_桥式整流器/AC电压源”。模型中线性或开关线性网络的数量为0。模型中的非线性网络数为1。ans=1×1单元阵列{'ssc_桥式整流器/交流电压源}模型包含交流电压源块,产生非线性方程的周期源。

您可以通过添加Simscape来替换Simscape周期源受控电压源利用Simulink实现Simscape网络中的块金宝app正弦波在网络之外阻塞。另一个好处是,您可以配置正弦波实时模拟期间在运行时阻塞。

删除交流电压源块。

添加正弦波从Simulink Sourc金宝appes库中获取。

添加金宝appSimulink-PS转换器块从Simscape实用程序库。

添加受控电压源阻止从Simscape / Foundation Library / Electrical / Electrical Sources库。

连接正弦波块的金宝appSimulink-PS转换器街区与城市金宝appSimulink-PS转换器块的受控电压源块。

Simu金宝applink模型配置为可变步长仿真。如果指定正弦波块采样时间为

-1,为继承采样时间,仿真生成警告。的示例时间正弦波作为0通过使用工作空间变量,您可以稍后调整该变量以提高模拟速度或精度交流电压源块有一个峰值振幅的sqrt(2)*120V和一个频率的60赫兹.配置正弦波块。

在工作区中定义示例时间。

Ts = 1 e-5;

设定振幅参数

sqrt(2)*120.设定频率(rad /秒)参数

60 * 2 *π.设定样品时间参数

Ts.

确保没有区块导致网络非线性。

%模拟sim (baselineModel)%检查非线性块simscape.FindOnlinearBlock(基线模型)

模型中线性或交换线性网络的数量为1。Ans = 0×0空单元格数组

该模型仅包含产生线性或切换线性方程组的块。

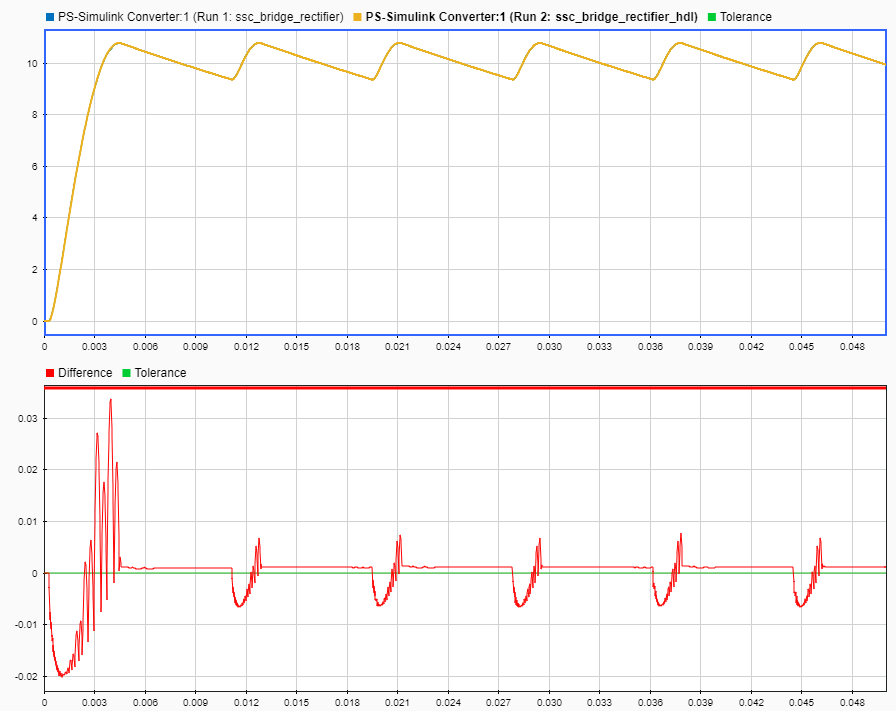

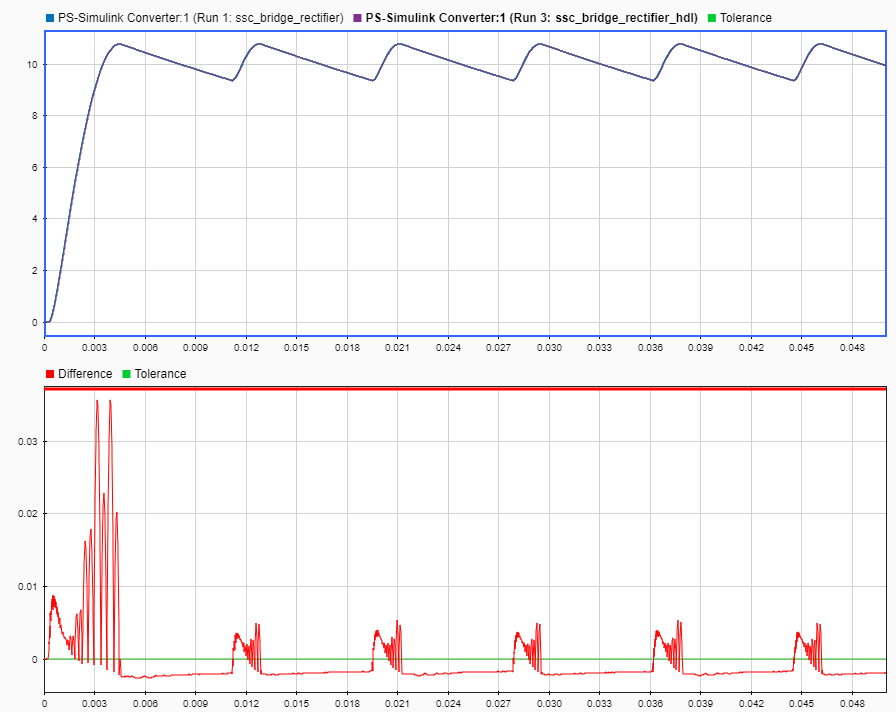

在模拟数据检查器中模拟模型并将结果与基线结果进行比较。

%获取模拟数据检查器运行idrunIDs = 金宝appSimulink.sdi.getAllRunIDs;runBaseline = runid (end - 1); / /结束runSwitchedLinear = runIDs(结束);%打开模拟数据检查器金宝appSimulink.sdi.view compBaseline1=Simulink.sdi.compareRuns(运行基线,...runSwitchedLinear);

结果与基线结果相似。

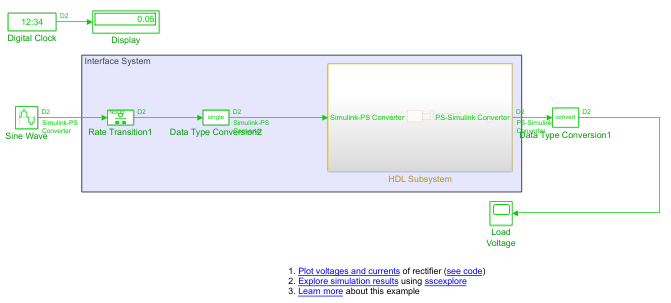

为了稍后检查Simscape HDL Workflow Advisor的进度,添加并连接一个数字时钟从Simulink源代码库和一金宝app个显示块,如图所示。金宝app为数字时钟,指定

Ts为样品时间参数

该模型目前正在使用变步长求解器在连续时间内进行模拟。对于实时仿真,离散时间仿真需要固定步长求解器。示例时间颜色和注释可以帮助您确定模型是否包含任何连续设置。控件上的Simulink模型窗口中打开示例时间颜色和注释金宝app调试选项卡,在信息覆盖,在样品时间组,选择颜色和文本.

模型图将更新,并显示采样时间图例。

为实时仿真配置模型。

为固定步长、固定成本的仿真配金宝app置Simulink模型。在模型配置参数中,为解算器参数设置:

集类型来

固定步.集解算器来

离散(无连续状态).

为固定步长、固定成本模拟配置Simscape网络。为解算器配置布洛克:

选择使用本地解算器.

确保解算器类型设置为

向后欧拉.具体说明

Ts对于样品时间.

在模拟数据检查器中模拟模型并将结果与基线结果进行比较。

%模拟sim (baselineModel)%获取模拟数据检查器运行idrunIDs = 金宝appSimulink.sdi.getAllRunIDs;runBaseline = runid (end - 2); / /结束runRealTime = runIDs(结束);%打开模拟数据检查器金宝appSimulink.sdi.view compBaseline1=Simulink.sdi.compareRuns(运行基线,...运行时间);

结果与基线结果相似。

生成HDL代码使用模拟风景HDL工作流顾问

通过在您一步步准备的Simscape模型上运行Simscape HDL Workflow Advisor来生成HDL代码模型制备或者在已经准备好代码生成的Simscape模型上。

重命名模型。

要继续使用为HDL代码生成准备的模型,请重命名该模型

ssc_模型.要打开和使用已经为HDL代码生成准备好的模型,请在MATLAB命令提示符处输入

开放式系统(“ssc_bridge_rectifier_hdl”)将模型保存到本地目录为

ssc_模型.

运行Simscape HDL Workflow Advisor。

sschdladvisor (“ssc_模型”)打开Simscape HDL Workflow Advisor。

运行代码生成兼容性检查。

选择代码生成兼容性>检查解算器配置然后点击运行此任务.

选择检查切换线性然后点击运行此任务.

advisor会报告您的模型何时通过了这些检查。

提取状态空间系数。选择状态空间转换>获取状态空间参数然后点击运行此任务.转换可能需要一些时间。的显示块显示经过的模拟时间。

运行任务后,advisor将显示状态空间表示形式的摘要和参数表。

状态数:5

输入个数:1

输出数量:1

模式数:7

离散采样时间:1e-05

参数 参数的大小 一个 5 x 5 x 7 B 5 x 1 x 7 F0 5 x 1 x 7 C 1 x 5 x 7 D 1 x 1 x 7 Y0 1 x 1 x 7 状态、模式和参数数据的大小可以帮助您估计部署模型需要多少FPGA资源。数值越大,需要的FPGA资源越多。输入和输出数据表明了实时部署和可视化所需的I/O连接的数量和类型。

生成模型的HDL实现。选择实现模型生成>生成实现模型然后点击运行此任务.

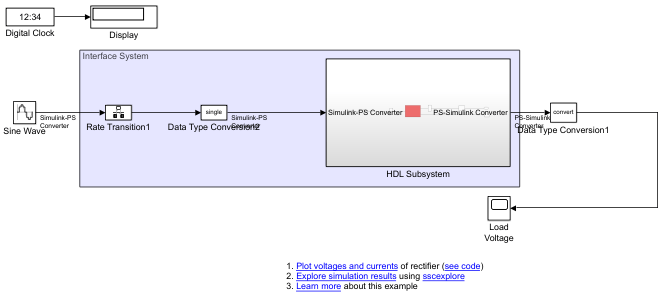

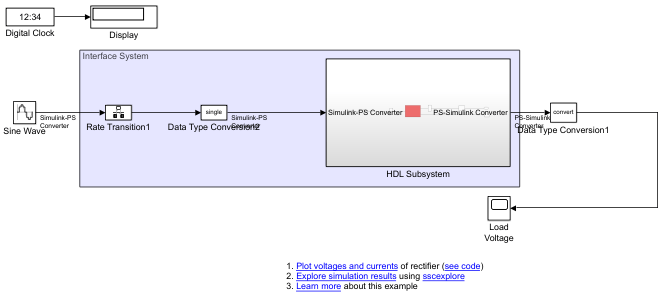

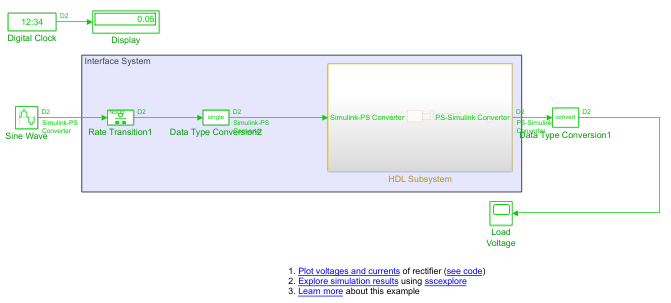

当生成实现模型时,advisor报告已经传递了任务,并显示到生成的实现模型的链接,该实现模型名为GMStateSpace HDL_ssc_模型.

通过单击提供的链接打开生成的实现模型。

模型包含标记为:

子系统- 金宝appSimulink子系统,包含准备好的模型和Simscape HDL Workflow Advisor添加的任何信号路由。对于这个模型,advisor添加一个转到路经的街区正弦波块输入到高密度脂蛋白子系统.

T- - - - - -从…起路经的街区正弦波块输入子系统块的高密度脂蛋白子系统块。

率Transition1-处理以不同速率运行的块之间的数据传输。

数据类型Conversion1-将双数据类型转换为单数据类型,这是生成HDL代码所必需的。

高密度脂蛋白子系统-金宝appSimulink子系统,包含与Simscape网络兼容的HDL代码生成版本。对于这个模型,advisor添加一个转到路经的街区正弦波块输入到高密度脂蛋白子系统块。

范围—显示负载电压。

准备高密度脂蛋白子系统对于与基线结果的模拟比较:

删除T从…起块。

复制粘贴正弦波块的子系统将块插入顶级模型。

连接正弦波块的率Transition1块。

删除子系统块,其中包含基线模型。

在仿真数据检查器中为进入的信号启用数据记录范围块。

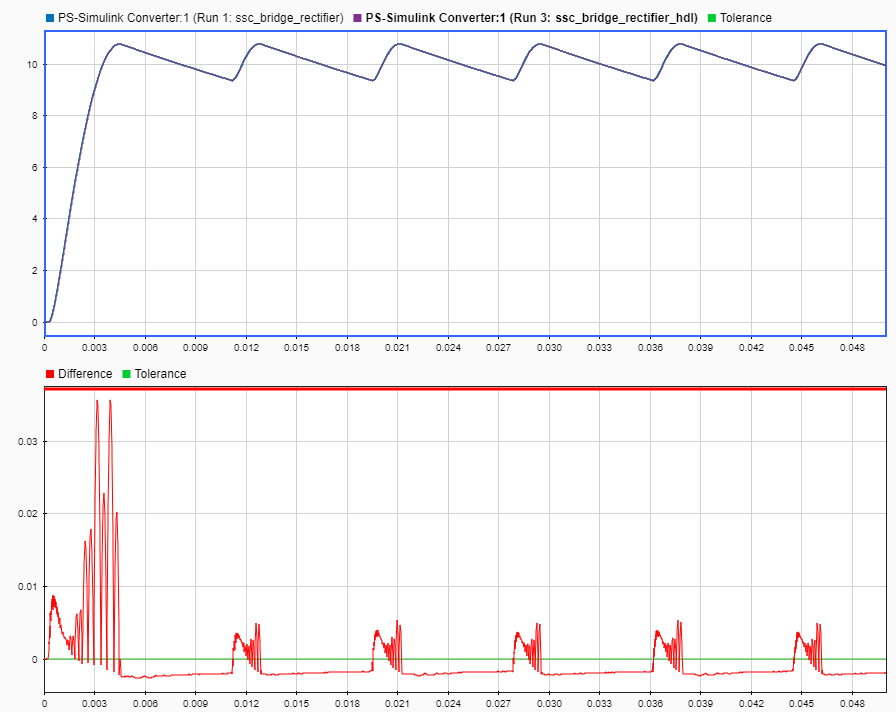

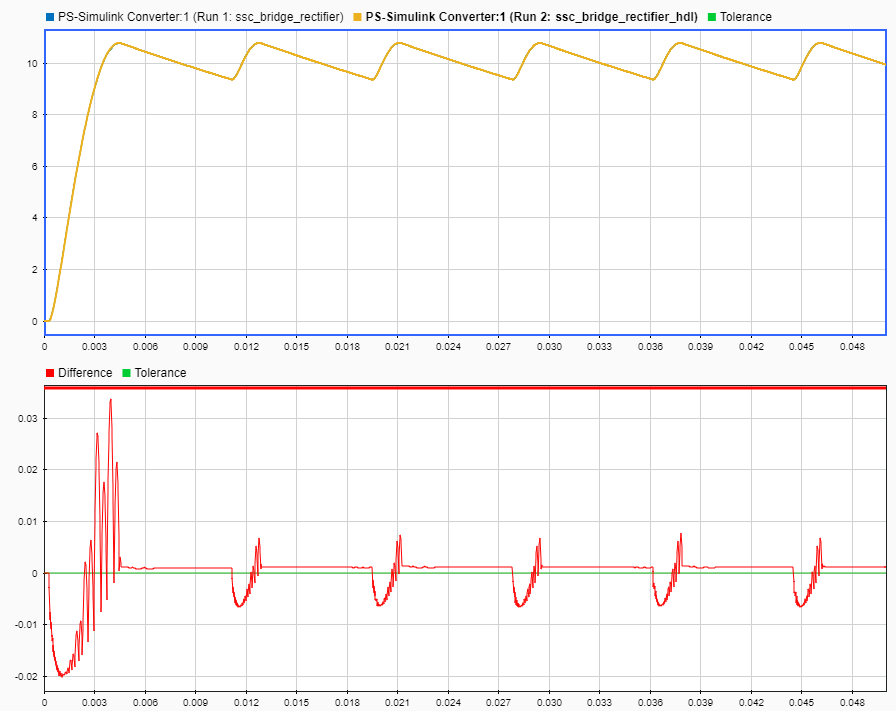

为了确保HDL子系统与原始Simscape模型相对应,模拟该模型并将结果与基线模拟结果进行比较。

%模拟sim卡(“gmStateSpaceHDL_ssc_model”)%获取模拟数据检查器运行idrunIDs=Si金宝appmulink.sdi.getAllRunIDs;runBaseline=runid(end-3);runHDLImplementation=runIDs(结束);%打开模拟数据检查器金宝appSimulink.sdi.view compBaseline1=Simulink.sdi.compareRuns(运行基线,...Runhdlimpmentation);

结果与基线结果相似。您的Simscape模型现在被转换为一个与HDL代码生成兼容的实现。

从实现生成HDL代码:

在模型配置参数中,为HDL代码生成报告,选择生成可追溯性报告和生成资源利用率报告选项。

运行

hdlsetup函数。hdlsetup(“gmStateSpaceHDL_ssc_model”)保存模型和子系统参数设置。

hdlsaveparams (“gmStateSpaceHDL_ssc_model”);%%设置模型“gmStateSpaceHDL_ssc_模型”HDL参数hdlset_参数(“gmStateSpaceHDL_ssc_模型”、“FloatingPointTargetConfiguration”、…hdlcoder.createFloatingPointTargetConfig(“NativeFloatingPoint”);hdlset_参数(“gmStateSpaceHDL_ssc_模型”、“MaskParameterAsGeneric”、“on”);hdlset_参数(“gmStateSpaceHDL_ssc模型”、“过采样”,100);%设置子系统HDL参数hdlset_param('gmStateSpaceHDL_ssc_model/HDL SubSystem','flatthierarchy','on');

保存验证模型生成设置。

HDL模型名=“gmStateSpaceHDL_ssc_model”;hdlset_param (HDLmodelname“GenerateValidationModel”,“上”);

生成HDL代码。

makehdl (“GMStateSpace HDL\u ssc\u模型/HDL子系统”)###为“gmStateSpaceHDL_ssc_model/HDL子系统”生成HDL。### Using the config set for model gmStateSpaceHDL_ssc_model…用于HDL代码生成参数。###启动HDL检查。###代码生成和优化选项…已经导致了额外的管道延迟。###延迟平衡功能已经自动插入…匹配补偿延迟。### DUT需要一个初始管道设置延迟. ...每个输出端口都会经历这些额外的延迟。 ### Output port 0: 1 cycles. ### Clock-rate pipelining results can be diagnosed by running this script:... C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\highlightClockRatePipelining.m ### One or more feedback loops in the model are inhibiting optimizations. ... To highlight these loops in your model, click the following MATLAB ... script: C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\highlightFeedbackLoop.m ### To clear highlighting, click the following MATLAB ... script: C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\clearhighlighting.m ### Generating new validation model: gm_gmStateSpaceHDL_ssc_model_vnl. ### Validation model generation complete. ### Begin VHDL Code Generation for 'gmStateSpaceHDL_ssc_model'. ### MESSAGE: The design requires 100 times faster clock ... with respect to the base rate = 2e-07. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode ... Selection/Mode Vector To Index/Subsystem1 ... as C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_mul_comp ... as C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\nfp_mul_comp.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_add_comp ... as C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\nfp_add_comp.vhd. ### Working on MultiplyAndAdd_2_entries ... as C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\MultiplyAndAdd_2_entries.vhd. ### Working on MultiplyAndAdd_1_entries ... as C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\MultiplyAndAdd_1_entries.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_uminus_comp ... as C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\nfp_uminus_comp.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_relop_comp ... as C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\nfp_relop_comp.vhd. ### Working on HDL Subsystem_tc ... as C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\HDL_Subsystem_tc.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem ... as C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\HDL_Subsystem.vhd. ### Generating package file ... C:\Temp\hdlsrc\gmStateSpaceHDL_ssc_model\HDL_Subsystem_pkg.vhd. ### Generating HTML files for code generation report ... at gmStateSpaceHDL_ssc_model_codegen_rpt.html ### Creating HDL Code Generation Check Report HDL_Subsystem_report.html ### HDL check for 'gmStateSpaceHDL_ssc_model' complete ... with 0 errors, 0 warnings, and 3 messages. ### HDL code generation complete.

HDL代码生成报告将打开,并包含所有生成的错误或警告。该报告包含指向资源利用率报告的链接,该报告描述了FPGA部署的资源需求。

生成的HDL代码和验证模型保存在hdlsrc \ gmStateSpaceHDL_ssc_model \ html目录生成的代码另存为HDL_Subsystem_tc.vhd.

要生成用于部署到指定目标的HDL代码,请使用HDL Workflow Advisor。

另请参阅

阻碍

Simscape块

功能

simscape.FindOnlinearBlock|HDL遮阳板(高密度脂蛋白编码器)|hdlsaveparams(高密度脂蛋白编码器)|hdlset_param(高密度脂蛋白编码器)|hdlsetup(高密度脂蛋白编码器)|makehdl(高密度脂蛋白编码器)|sschdladvisor(高密度脂蛋白编码器)

相关的例子

- 查看样本时间信息

- 为Simscape模型生成HDL代码(高密度脂蛋白编码器)

- 为Simscape金宝app二电平变流器模型生成Simulink实时接口子系统(高密度脂蛋白编码器)

- Simscape直流电机控制到兼容hdl的Simulink模型的故障诊断转换金宝app(高密度脂蛋白编码器)

- Simscape永磁同步电机到hdl兼容Simulink模型的故障诊断转换金宝app(高密度脂蛋白编码器)

- 在模拟数据检查器中查看数据

更多关于

- HDL工作流顾问入门(高密度脂蛋白编码器)

- 创建和使用代码生成报告(高密度脂蛋白编码器)

- 半实物仿真的工作流

- 实时模型准备工作流程

- 实时仿真的工作流