数据采集流程

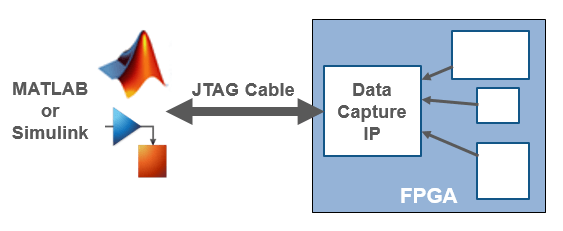

当设计在FPGA上运行时,使用FPGA数据捕获来观察来自设计的信号。该功能从FPGA捕获信号数据窗口,并将数据返回到MATLAB®或仿真金宝app软件®.

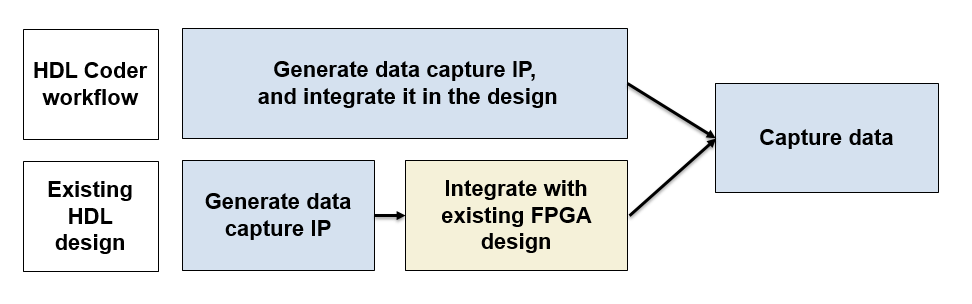

有两个工作流程从FPGA板捕获数据到MATLAB或Simulink:金宝app

当您使用HDL Coder™生成HDL IP时,请使用HDL Workflow Advisor生成数据捕获IP并将其集成到设计中。

如果您有一个现有的HDL设计,HDL验证器™提供工具来生成数据捕获IP。然后,手动将生成的IP集成到FPGA设计中。

为了从你的设计中捕获信号,HDL验证器生成一个与MATLAB通信的IP核。在您的设计中使用HDL Coder工作流来自动集成数据捕获IP核。否则,请手动将此IP核集成到您的HDL项目中,并将其与其余设计一起部署到FPGA中。然后,使用以下方法之一来捕获数据。

为了捕获数据到MATLAB - HDL验证器生成一个定制的应用程序,返回捕获的信号数据。或者,您可以使用生成的System对象™以编程方式捕获数据。

为了捕获数据到Simulink - HDL验金宝app证器生成一个块,该块具有与您捕获的信号相对应的输出端口。

在这两种情况下,您都可以为捕获的数据指定数据类型、要捕获的窗口数量和控制数据采样时间的触发条件。

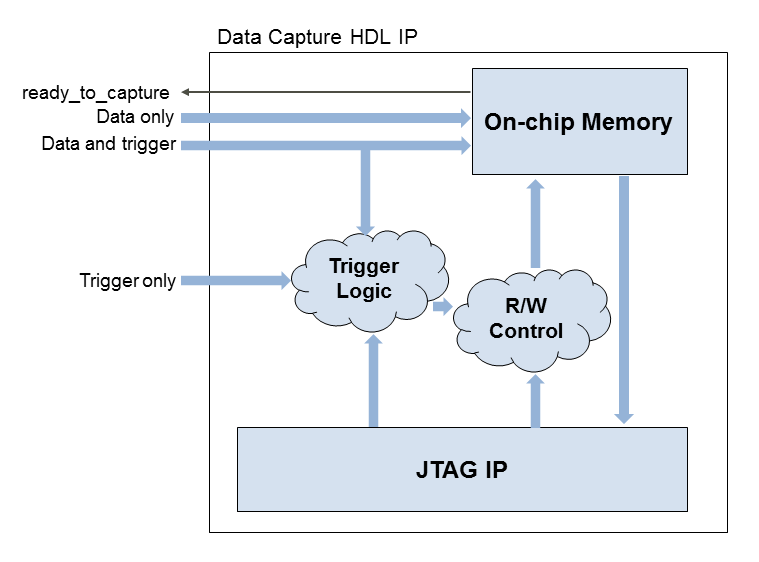

当设计在FPGA上运行时,首先生成的IP核等待您指定的触发器条件。通过在一个或多个信号上匹配的特定值定义触发器条件。当检测到触发器时,逻辑将指定的信号捕获到缓冲区,并通过JTAG接口将数据返回给主机。然后,您可以在MATLAB工作空间或Simulink模型中分析和显示这些信号。金宝app

使用HDL工作流顾问生成和集成数据捕获IP

当你使用高密度脂蛋白工作流顾问要生成您的HDL设计,首先在Simulink中标记有趣的信号作为测试点。金宝app使用以下方法配置设计高密度脂蛋白工作流顾问:

通过选择为测试点启用HDL DUT端口生成选项设置目标接口的一步。有关更多信息,请参见设置目标接口(高密度脂蛋白编码器).

连接测试点信号到FPGA的数据捕获- JTAG接口设置目标接口的一步。

控件中设置数据收集所需的缓冲区大小和最大序列深度生成RTL代码和IP核的一步。有关更多信息,请参见生成RTL代码和IP核(高密度脂蛋白编码器).

然后,运行其余步骤来为您的设计生成HDL并对FPGA编程。数据捕获IP核集成在生成的设计中。现在你已经准备好了捕获数据.

为现有的HDL设计配置和生成IP核

在捕获FPGA数据之前,首先指定要捕获哪些信号,以及要返回多少样本。使用FPGA数据捕获组件生成器来配置这些和其他设置,并生成HDL IP核。IP核心包括:

要捕获或使用的每个信号的端口,作为触发条件的一部分

用于捕获每个信号所需的样本数量的存储器

JTAG接口逻辑与MATLAB进行通信

可以在运行时配置的触发器逻辑

一种准备捕获的信号,用于从FPGA控制数据流

该应用程序还生成一个定制的FPGA数据捕获应用程序、系统对象和与FPGA通信的模型。

IP集成到FPGA中

为了使MATLAB与FPGA通信,必须将生成的HDL IP核集成到FPGA设计中。如果你使用高密度脂蛋白工作流顾问为了生成您的数据捕获IP,这个步骤是自动的,并且数据捕获IP操作一个单时钟速率,这是您的待测设计(DUT)的主时钟。否则,请按照生成报告中的说明操作。将生成的HDL文件添加到hdlsrc文件夹到FPGA项目中。然后,实例化HDL IP核,datacapture,并将其连接到您请求捕获和触发的信号。用新图像编译项目并对FPGA进行编程。

捕获数据

FPGA数据捕获IP核通过FPGA板和主机之间的JTAG电缆通信。确保线缆已连接。在捕获数据之前,您可以为捕获的数据设置数据类型,并设置触发器条件来指定捕获数据的时间。要配置这些选项并捕获数据,您可以:

打开FPGA数据捕获设置触发器和数据类型参数,然后将数据捕获到MATLAB工作区中。

派生的生成的System对象

hdlverifier。FPGADataReader.使用System对象的方法和属性设置数据类型和触发器条件,然后调用对象来捕获数据。在Si金宝appmulink中,打开生成的模型并配置参数FPGA数据阅读器块。然后运行模型来捕获数据。

捕获数据并将其导入MATLAB工作空间或Simulink模型后,就可以分析、验证和显示数据了。金宝app

另请参阅

FPGA数据捕获|FPGA数据捕获组件生成器|FPGA数据阅读器|hdlverifier。FPGADataReader