Vision HDL工具箱中的每个时钟多像素处理

杰克·埃里克森MathWorks

低延迟视频处理应用依赖于FPGA和ASIC硬件来处理大量传入的像素数据。但4k和8k等高分辨率格式以及高帧率视频每秒包含的像素太多,无法连续处理。数字硬件允许并行,但许多算法,如滤波器和边缘检测操作在一个窗口的连续像素,这使得有效的并行处理具有挑战性。

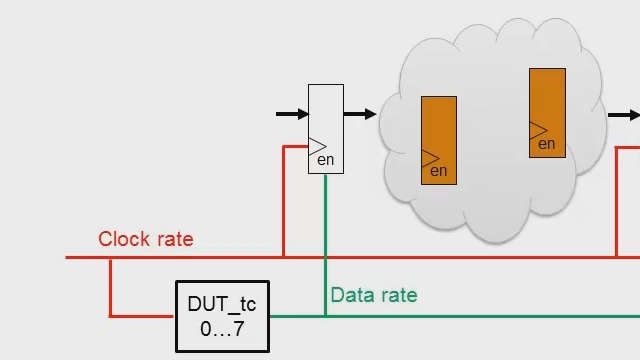

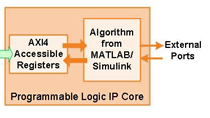

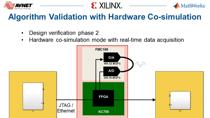

Vision HDL Toolbox™本机支持每个时钟多像金宝app素处理。它的帧到像素和像素到帧网关块提供了简单的设置,以切换设计的输入和输出,从一个像素一次到4或8个并行。金宝app支持的算法,如本例中显示的图像滤波器和边缘检测块,会根据指定的并行级别自动更新它们的架构。它们用适当的延迟来模拟这种行为,并使用HDL Coder™生成可合成的RTL,在这些重叠的邻域处理窗口之间共享资源。结果是,资源的使用与每个时钟的像素数呈亚线性关系。

要利用这种能力开发定制的每个时钟多像素算法,请使用Line Buffer块,如中所示这个视频。