HDL编码器教程和评估参考指南

居里夫人这周选的是——实际上,是复数!我选择的是高密度脂蛋白编码器教程和HDL编码器评估参考指南,均由杰克·艾里克森.

如果您不知道,您可以从MATLAB和Simulink生成HDL(硬件描述语言)代码来编程定制FPGA或ASIC硬件。我曾与第一次瞄准FPGA的客户合作,这些客户拥有数十年的ASIC设计经验,他金宝app们希望将芯片设计工作流程与基于模型的设计相结合,以提高灵活性和效率。

一个强大的工具,如HDL编码器意味着有一个学习曲线,特别是如果你是新的Simulink。金宝app为了帮助你开始,本教程提供了如何使用这个示例MATLAB代码的一步一步的指导:

关联Rx过滤器与匹配过滤器FilterOut=过滤器(CorrFilter,1,RX信号);找到峰值的大小和位置[peak, location] = max(abs(FilterOut));

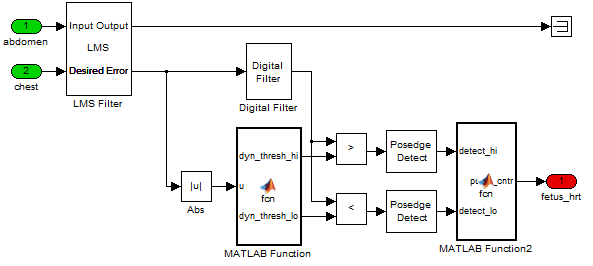

到Simu金宝applink架构,定点模型,准备生成VHDL或Verilog:

学习基于模型的设计工具与理解FPGA/ASIC硬件上的目标算法设计过程同样重要。

因此,在完成本教程后,您将感到有能力在Simulink中开始下一个HDL设计。金宝app但您仍然有许多问题:“创建高效硬件的最佳实践是什么?”“如何指导工具使用FPGA资源,如RAM和DSP块?”“我不知道如何模拟我的时钟信号!””(你不)。

这些问题的答案,以及我们用户中的许多其他热门话题都在HDL编码器评估参考指南.这份28页的文档描述了产生高效HDL代码的设计模式和设置,并重点介绍了有助于加快设计过程的有用工具。

例如,您将学习如何使本地启用信号同步行为;用逻辑分析仪范围查看时序图;并使用MATLAB函数块将MATLAB代码合并到你的Simulink设计金宝app中——当涉及到控制逻辑时非常方便。

是的,有一整节专门介绍FPGA资源映射,例如Xilinx®和Intel®FPGA上映射到DSP块的复杂乘法器:

所以不要被页数吓到,开始阅读吧!(事实上,其中一半是照片)。如果你想评估特定于你的HDL设计的能力,我的同事和我期待着与你合作。

试试看,让我们知道你的想法在这里!

发布与MATLAB®R2019a

- 类别:

- 选择

克里夫角:克里夫·摩尔论数学与计算

克里夫角:克里夫·摩尔论数学与计算 罗兰关于MATLAB的艺术

罗兰关于MATLAB的艺术 用MATLAB进行图像处理

用MATLAB进行图像处理 Simulin金宝appk上的家伙

Simulin金宝appk上的家伙 深度学习

深度学习 开发区

开发区 斯图尔特的MATLAB视频

斯图尔特的MATLAB视频 在标题后面

在标题后面 本周文件交换精选

本周文件交换精选 物联网上的汉斯

物联网上的汉斯 学生休息室

学生休息室 创业公司、加速器和企业家

创业公司、加速器和企业家 MATLAB社区

MATLAB社区 MATLABユーザーコミュニティー

MATLABユーザーコミュニティー

评论

要留下评论,请点击在这里登录到您的MathWorks帐户或创建一个新帐户。