英特尔SoC设备

在Intel上生成和部署HDL代码和嵌入式软件®SoC设备

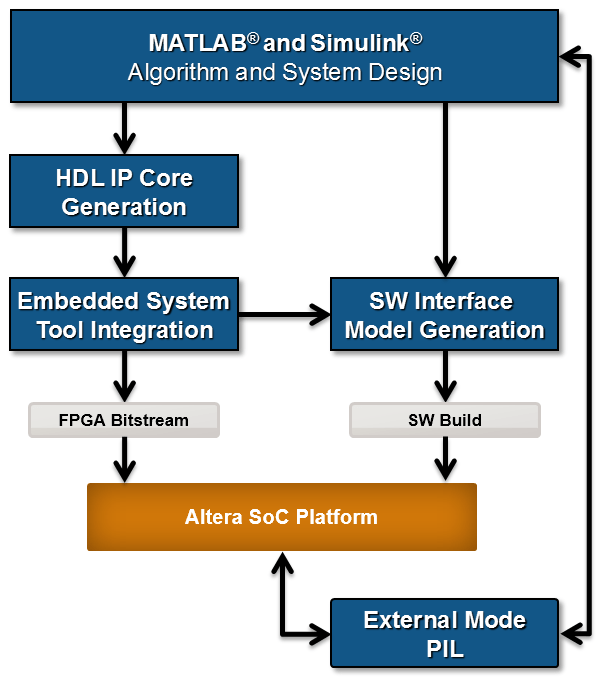

HDL Coder™可以生成一个IP核,将其集成到您的Qsys项目中,并对英特尔硬件进行编程。使用嵌入式编码器®,你可以生成和构建嵌入式软件,并在ARM上运行它®处理器。看到SoC平台的软硬件协同设计工作流程.

若要将设计部署到Intel SoC设备,必须安装Intel SoC设金宝app备的HDL编码器支持包.有关安装信息,请参见HDL编码器支持的硬金宝app件.

类

功能

主题

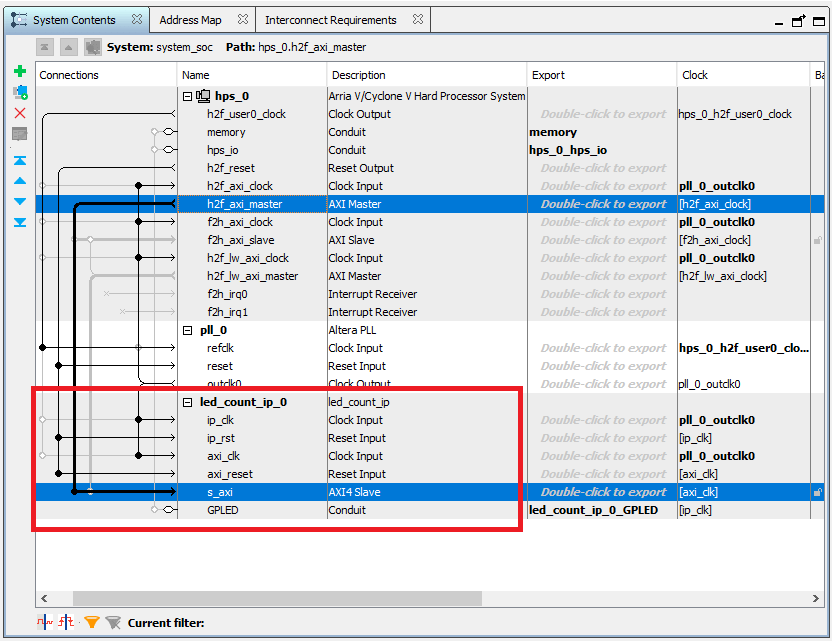

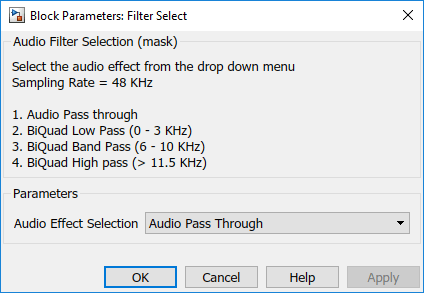

如何为标量、向量端口、总线数据类型和回读值的AXI4或AXI4- lite接口设计模型。

如何为ax4 - stream矢量或标量接口生成设计模型。

描述AXI4主协议,以及如何使用AXI4-Master接口设计IP核生成模型。

如何对目标英特尔或Xilinx硬件进行编程。

故障排除

解决IP核生成和Simulink实时FPGA I/O工作流程中的时序故障金宝app

解决IP Core Generation Workflow或Simulink Real-Time FPGA I/O Workflow for Vivado-Based boa金宝apprd中的Build FPGA Bitstream步骤中的时序故障。