独立FPGA板

要在独立英特尔或Xilinx FPGA板上部署您的设计,必须安装HDL编码器™ 英特尔金宝appFPGA板支持包或者Xilinx FPG金宝appA板的HDL编码器支持包分别。有关安装信息,请参阅支持HDL编码器的硬金宝app件。

班级

hdlcoder.Board |

董事会注册对象描述SoC Custom Board |

hdlcoder.ReferenceDesign |

描述SoC参考设计的参考设计注册对象 |

hdlcoder.WorkflowConfig |

配置HDL代码生成和部署工作流 |

职能

话题

IP核心生成

如何为标量,矢量端口,总线数据类型和读取值设计Axi4或Axi4-Lite接口模型。

如何设计AXI4流矢量或标量界面生成模型。

如何使用AXI4流视频接口设计IP核心生成模型。

描述AXI4主协议,以及如何使用AXI4主接口设计IP核心生成模型。

了解如何在独立FPGA设备上使用IP核心生成工作流,并将IP核心嵌入参考设计中。

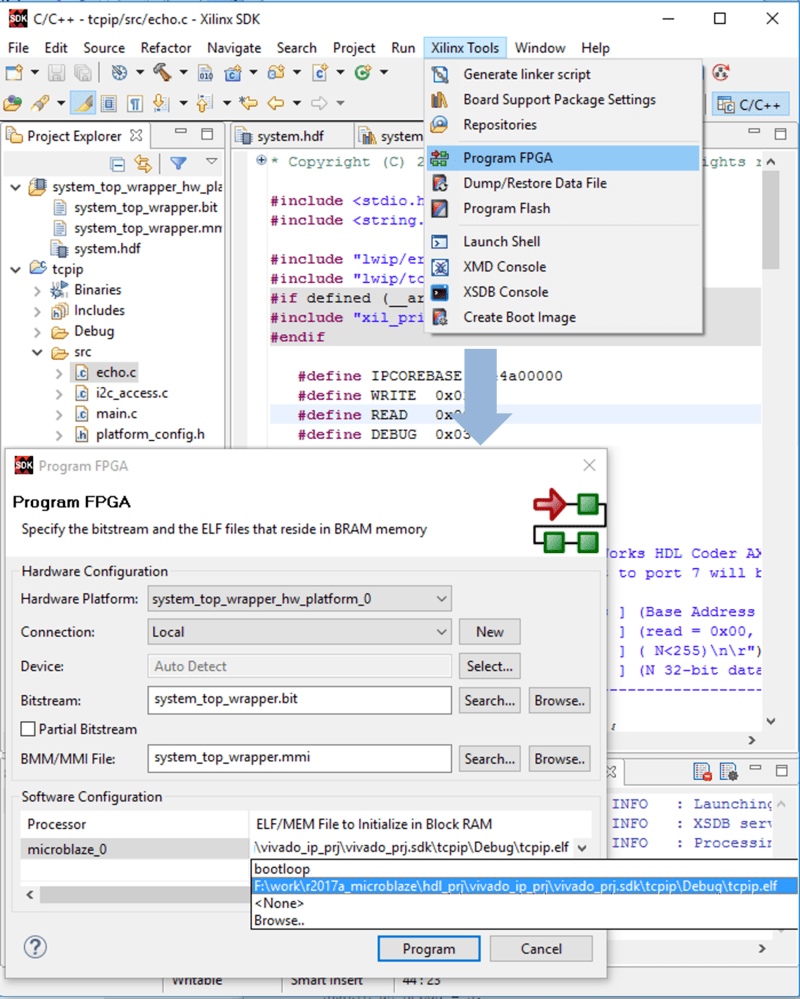

程序Xilinx和Intel板

如何编程目标英特尔或Xilinx硬件。

从Simulink为独立Xilinx FPGA开发板编程金宝app(适用于Xilinx 金宝appFPGA板的HDL编码器支持包)

本例显示了如何使用FPGA交钥匙工作流程将Xilinx FPGA开发板作为合成目标。

Simulink的独立Altera FPGA开发板金宝app(英特尔FPGA板的H金宝appDL编码器支持包)

此示例显示了如何定位Altera®FPGA开发板综合使用FPGA交钥匙工作流程。

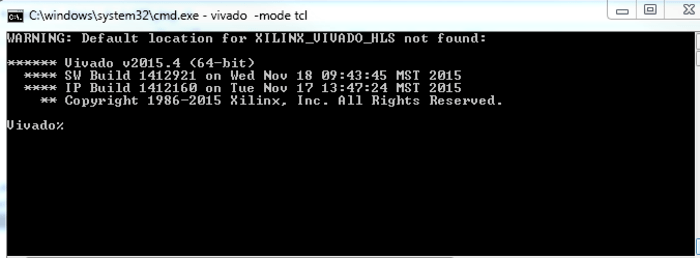

从Matlab编程独立Xilinx FPGA开发板(适用于Xilinx 金宝appFPGA板的HDL编码器支持包)

用于部署到独立FPGA硬件的FPGA交钥匙工作流程。

从Matlab进行独立Altera FPGA开发板(英特尔FPGA板的H金宝appDL编码器支持包)

用于部署到独立FPGA硬件的FPGA交钥匙工作流程。

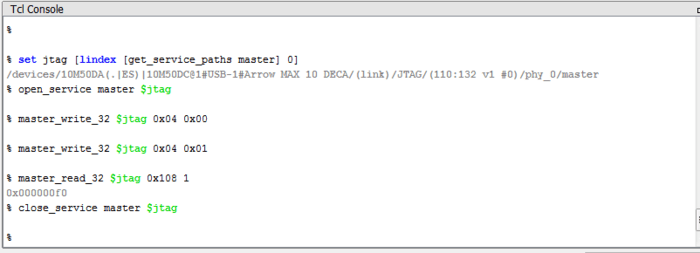

故障排除

解决IP核心生成和Simulink实时FPGA I/O工作流中的定时故障金宝app

解决基于Vivado的电路板的IP核心生成工作流程的构建FPGA比特流步骤的时序故障或基于Vivado的板的Simulink实时FPGA I / O工作流程。金宝app