主要内容

内存事务

在SoC模型中创建共享内存系统

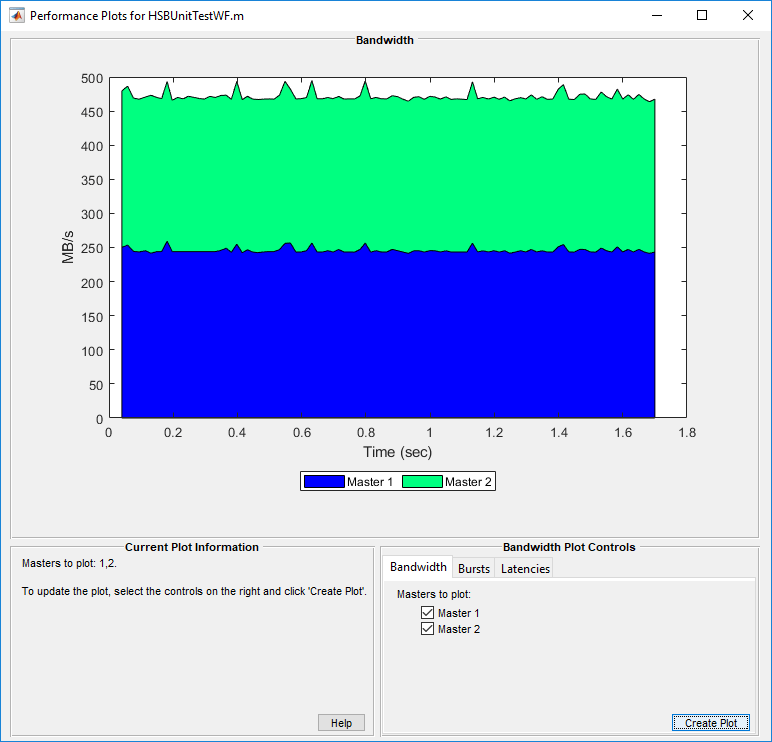

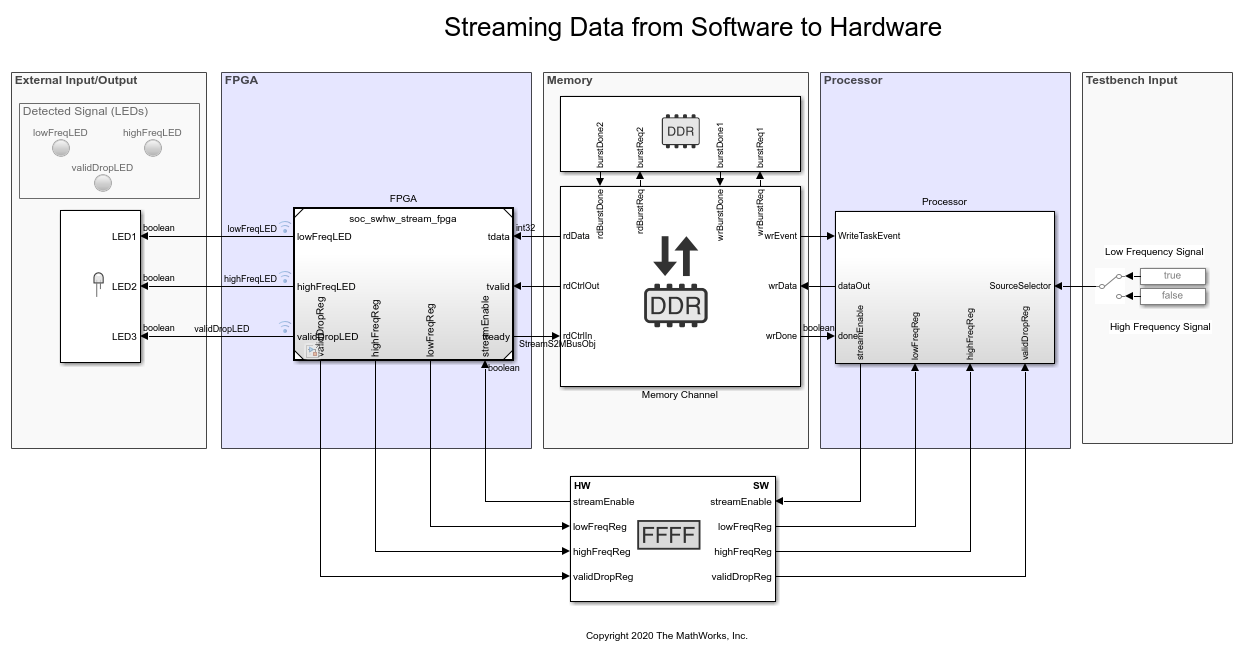

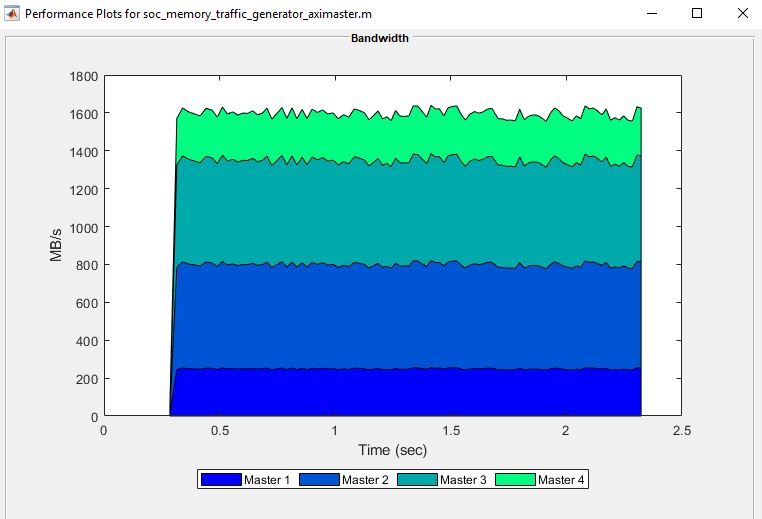

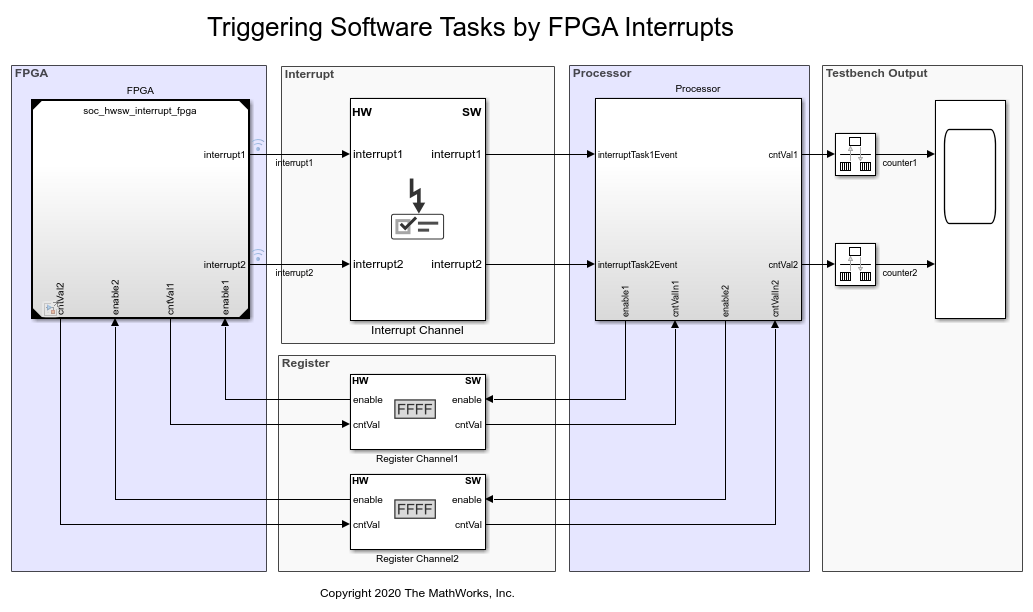

SoC Blockset™支持在Simulink中模拟和评估共享内存事务金宝app®. 要在SoC模型中包括内存系统,请为所需数量的内存通道配置内存控制器,然后将控制器连接到内存通道块,以仲裁和处理内存流量。

块

金宝appSimulink配置参数

话题

内存和寄存器传输简介。

金宝app支持的内存通道协议和控制信号。

如何为AXI4流向量或标量接口生成设计模型。

AXI4 Master协议的描述,以及如何使用AXI4-Master接口设计用于IP核生成的模型。

如何设计带有axi4流视频接口的IP核生成模型。