内存

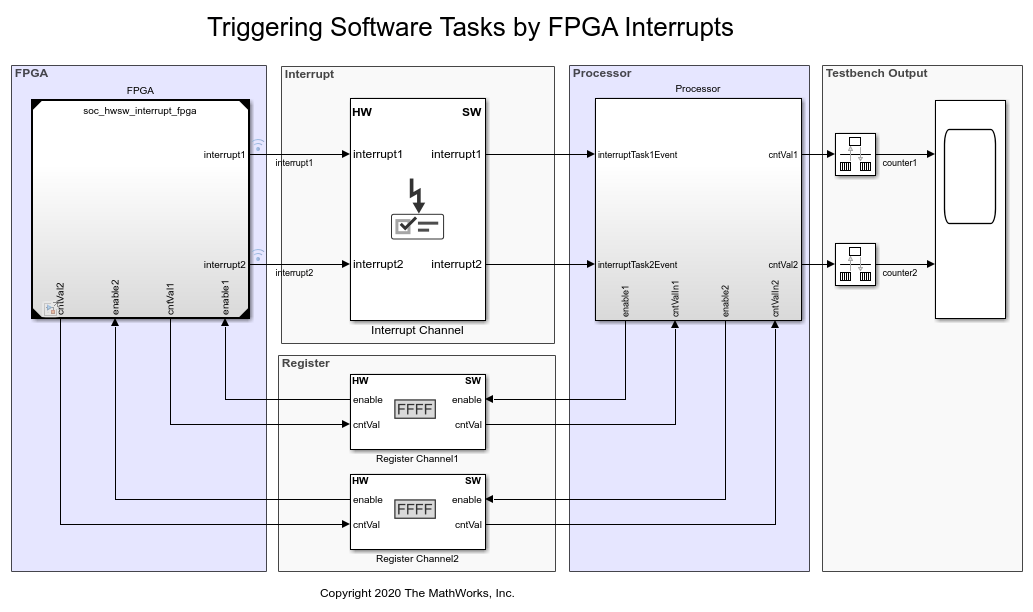

SoC Blockset™ enables simulation and evaluation of shared memory transactions in Simulink®. To include a memory system in your SoC model, configure a memory controller for the desired number of memory channels, and then connect the controller to memory channel blocks for arbitrating and handling memory traffic.

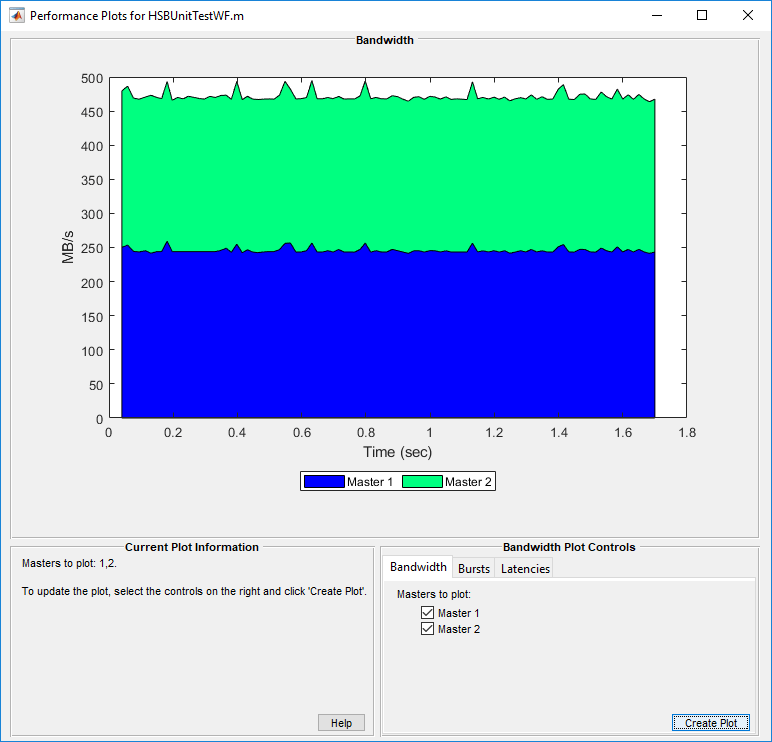

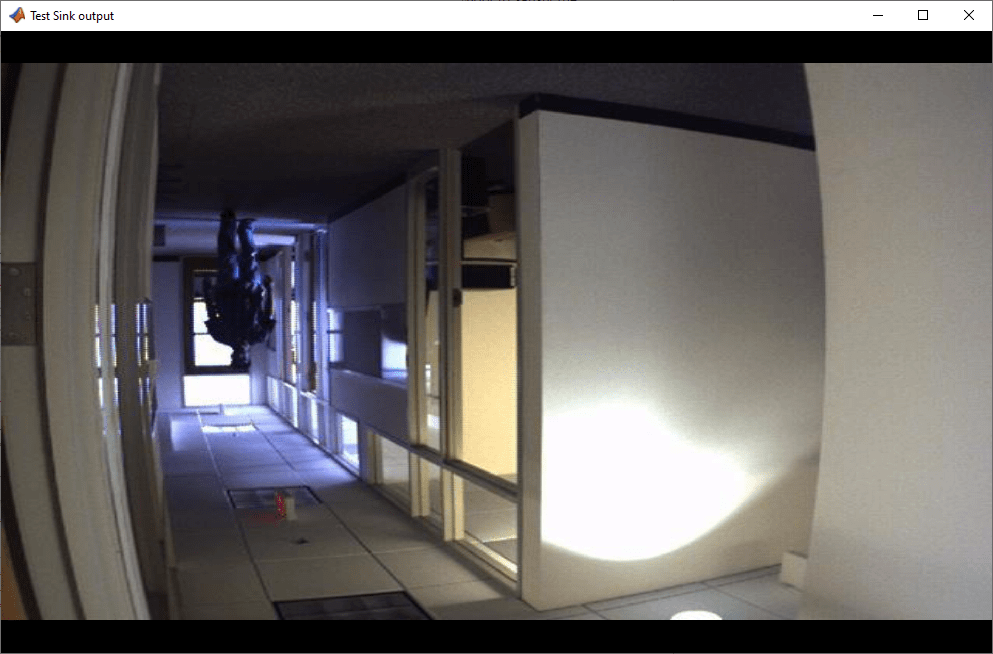

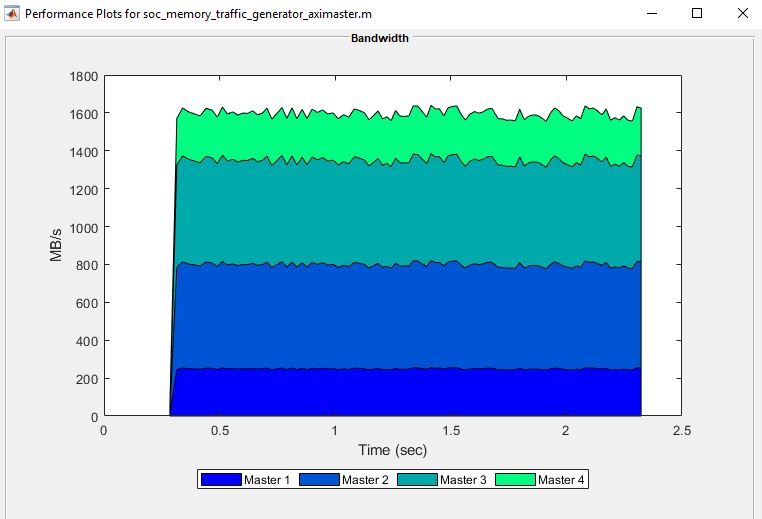

SoC Blockset enables the simulation and evaluation of shared memory transactions in Simulink. Visualize post-simulation performance and bandwidth metrics before deploying to SoC device by using theLogic Analyzer应用程序。

Blocks

Apps

| Logic Analyzer | Visualize, measure, and analyze transitions and states over time |

Tools

| 内存Mapper | Configure memory map for SoC application |

Simulink Configuration Parameters

Topics

Design

Introduction to memory and register transfers.

External Memory Channel Protocols

金宝app支持内存通道协议和控制团体nals.

How to design your model for AXI4-Stream vector or scalar interface generation.

Simplified AXI4 Master Interface

Description of AXI4 Master protocol, and how you can design your model for IP core generation with AXI4-Master interfaces.

How to design your model for IP core generation with AXI4-stream video interfaces.

Simulation

SoC Blockset enables simulation and evaluation of memory transactions in Simulink without the need to deploy a model to an SoC device.

Suggestions for enhancing simulation performance of SoC models.

SoC Blockset enables post-simulation analysis of memory diagnostic data.

Measurement

内存Performance Information from FPGA Execution

Obtain memory interconnect traffic information from a design running on FPGA.